# DesignWare ARC HS4xD Development Kit User Guide

Version 5818-001 April 2020

## **Copyright Notice and Proprietary Information Notice**

© 2020 Synopsys, Inc. All rights reserved. This Synopsys software and all associated documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the terms and conditions of a written license agreement with Synopsys, Inc. All other use, reproduction, modification, or distribution of the Synopsys software or the associated documentation is strictly prohibited.

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### **Disclaimer**

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **Trademarks**

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at

https://www.synopsys.com/company/legal/trademarks-brands.html.

All other product or company names may be trademarks of their respective owners.

#### **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

Synopsys, Inc. www.synopsys.com

# **Contents**

| Contents                                             | 3  |

|------------------------------------------------------|----|

| List of Figures                                      | 5  |

| List of Tables                                       | 6  |

| 1 Customer Support                                   | 7  |

| 1.1 Accessing SolvNetPlus                            | 7  |

| 1.2 Accessing ARC Application Notes                  | 7  |

| 1.3 Contacting the Synopsys Technical Support Center | 8  |

| 2 Introduction                                       | 10 |

| 2.1 Package Content                                  | 10 |

| 2.2 Getting Started                                  | 10 |

| 2.2.1 Installing Device Drivers                      | 10 |

| 2.2.3 Checking Default Board Settings                | 11 |

| 2.2.4 Installing and Configuring PuTTY               | 11 |

| 2.2.5 Starting U-Boot                                | 13 |

| 2.3 Location of Components On HSDK-4xD               | 14 |

| 2.4 Software Packages                                | 16 |

| 3 Hardware Description                               | 17 |

| 3.1 Overview of ARC HSDK-4xD                         | 17 |

| 3.2 Overview of ARC HS4xD Development System SoC     | 19 |

| 3.3 Clocks and Resets                                | 21 |

| 3.3.1 Clocks                                         | 21 |

| 3.3.2 Reset                                          | 24 |

| 3.4 Interrupts                                       | 26 |

| 3.5 Debug and Trace                                  | 32 |

| 3.5.1 Debug                                          | 33 |

| 3.5.2 ARC Real-Time Trace                            | 35 |

| 3.6 Configuration and Boot Modes                     | 36 |

| 3.6.1 Boot Switches                                  | 37 |

| 3.6.2 Jumpers                                        | 38 |

| 3.6.3 Other Switches                                 | 39 |

| 3.6.4 On-board LEDs                                  | 39 |

| DesignWare ARC HS4xD Development Kit User Guide    | Contents |

|----------------------------------------------------|----------|

| 3.7 Memories                                       |          |

| 3.8 USB Interface                                  | 40       |

| 3.9 Ethernet Interface                             | 40       |

| 3.10SD Card Interface                              | 41       |

| 3.11 Redpine® WiFi / Bluetooth Interface           | 41       |

| 3.12Audio Interface                                | 41       |

| 3.13On-board I2C Control Bus                       | 42       |

| 3.14ADC                                            | 42       |

| 3.15I/O Expander                                   | 43       |

| 3.16Extension Interfaces                           | 44       |

| 3.16.1 Digilent Pmod™                              | 45       |

| 3.16.2 Mikrobus                                    | 48       |

| 3.16.3 Arduino                                     | 49       |

| 3.16.4 HapsTrak3 Extension                         | 51       |

| 4 Programmer's Reference                           | 53       |

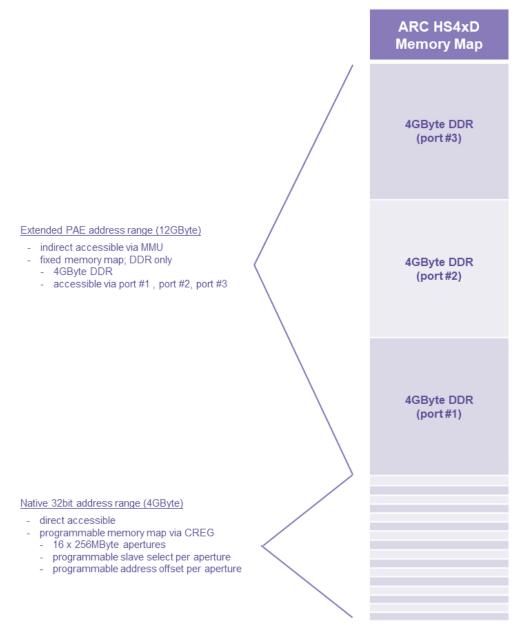

| 4.1 Memory Map                                     | 53       |

| 4.1.1 APB Peripheral Address Map                   | 54       |

| 4.1.2 PAE                                          | 56       |

| 4.1.3 I/O Coherency                                | 57       |

| 4.2 Software Interfaces                            | 58       |

| 4.2.1 Control Registers                            | 58       |

| 4.2.2 Clock Registers                              | 86       |

| 4.2.3 PWM Registers                                | 99       |

| Appendix A HapsTrak 3 Extension Connector Pins     | 116      |

| A.1 HapsTrak 3 Extension Connector Pin Description | 116      |

| Glossary and References                            | 118      |

| Glossary                                           | 118      |

| References                                         | 110      |

# **List of Figures**

| Figure 1 Identification of COM Port                                         | 11 |

|-----------------------------------------------------------------------------|----|

| Figure 2 PuTTY Configuration                                                | 12 |

| Figure 3 Application Boot with ARC HS47D Initialization                     | 13 |

| Figure 4 Linux Boot with ARC HS48x4 Initialization                          | 14 |

| Figure 5 HSDK-4xD Components- Top View                                      | 15 |

| Figure 6 HSDK-4xD Components: Bottom View                                   | 15 |

| Figure 7 ARC HSDK-4xD Block Diagram                                         | 17 |

| Figure 8 ARC HS4xD Development System SoC Top-Level Diagram                 | 19 |

| Figure 9 ARC HSDK-4xD Clock Architecture                                    | 21 |

| Figure 10 ARC HSDK-4xD Reset Architecture                                   | 25 |

| Figure 11 ARC HSDK-4xD Interrupt Architecture                               | 27 |

| Figure 12 ARC HSDK-4xD Debug and Trace Headers                              | 33 |

| Figure 13 JTAG Daisy Chain                                                  | 33 |

| Figure 14 10-Pin to 20-Pin JTAG Adapter                                     | 34 |

| Figure 15 ARC HSDK-4xD Configuration and Boot Switches and Buttons          | 36 |

| Figure 16 ARC HSDK-4xD Boot Switches                                        | 37 |

| Figure 17 ARC HSDK-4xD Peripheral Extension Interfaces                      | 44 |

| Figure 18 ARC HSDK-4xD HAPS Extension Interface                             | 44 |

| Figure 19 Pinout Diagram of the Pmod_A, Pmod_B and Pmod_C Connectors        | 45 |

| Figure 20 MikroBus Headers                                                  | 49 |

| Figure 21 Arduino Shield Interface                                          | 50 |

| Figure 22 ARC HSDK-4xD HAPS Extension: Typical Use-case                     | 52 |

| Figure 23 ARC HSDK-4xD Memory Map (After U-Boot)                            | 53 |

| Figure 24 ARC HS4xD Development System SoC Memory Map – High Level Overview | 56 |

| Figure 25 I/O Coherency Architecture                                        | 57 |

# **List of Tables**

| Table 1  | Overview of ARC HSDK-4xD Clock Components                        | 22  |

|----------|------------------------------------------------------------------|-----|

| Table 2  | ARC HSDK-4xD Interrupt Mapping                                   | 28  |

| Table 3  | ARC ID Codes                                                     | 34  |

| Table 4  | ARC HSDK-4xD Status and System LEDs                              | 39  |

| Table 5  | Ethernet Link Speed Indication                                   | 40  |

| Table 6  | I2S SCLK Divider Settings                                        | 41  |

| Table 7  | ARC HSDK-4xD On-board I2C Save Addresses                         | 42  |

| Table 8  | ADC Channel Usage                                                | 42  |

| Table 9  | I/O Expander I/O Overview                                        | 43  |

| Table 10 | Available Protocol Options                                       | 45  |

| Table 11 | Pin Description of the Pmod_A Connector                          | 46  |

| Table 12 | Pin Description of the Pmod_B Connector                          | 47  |

| Table 13 | Pin Description of the Pmod_C Connector                          | 48  |

| Table 14 | Pin Description of the MikroBUS Connectors                       | 49  |

| Table 15 | Pin Description of the Arduino Shield Interface                  | 51  |

| Table 16 | APB Peripheral Address Map                                       | 54  |

| Table 17 | CREG Control Register Overview                                   | 59  |

| Table 18 | CREG Address Decoder Register Reset Values (After U-Boot)        | 68  |

| Table 19 | GPIO Mux                                                         | 77  |

| Table 20 | CGU Clock Register Overview                                      | 86  |

| Table 21 | PWM Control Register overview                                    | 99  |

| Table 22 | Pin Description of the HapsTrak 3 Extension Connectors J3 And J4 | 116 |

Customer support is available through SolvNetPlus online customer support and through contacting the Synopsys Technical Support Center.

# 1.1 Accessing SolvNetPlus

SolvNetPlus includes an electronic knowledge base of technical articles and answers to frequently asked questions about Synopsys tools. SolvNetPlus also gives you access to a wide range of Synopsys online services, which include downloading software, viewing documentation on the Web, and entering a call to the Support Center.

To access SolvNetPlus:

- 1. Go to the SolvNetPlus Web page at http://solvnetplus.synopsys.com/.

- 2. If prompted, enter your user name and password. (If you do not have a Synopsys user name and password, follow the instructions to register with SolvNetPlus.)

If you need help using SolvNetPlus, click SolvNetPlus Help in the Support Resources section.

# 1.2 Accessing ARC Application Notes

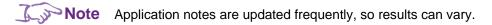

SolvNetPlus articles include useful application notes to help you do your job using DesignWare ARC products. To find application notes for your DesignWare ARC product, do the following:

- 1. Log into SolvNetPlus at https://solvnetplus.synopsys.com/.

- 2. Enter the name of your product in the **Search** field.

- Click Search.

The figure below shows example results.

# 1.3 Contacting the Synopsys Technical Support Center

Synopsys provides various methods for contacting Customer Support, as follows:

- For the fastest response, enter a case through SolvNetPlus:

- a. https://solvnetplus.synopsys.com

- b. Click the **Cases** menu and then click **Create a New Case** (below the list of cases).

- c. Complete the mandatory fields that are marked with an asterisk and click **Save**.

Make sure to include the following:

- Product L1: Select one of the following:

- DesignWare Cores ARC Tools

- DesignWare Cores ARC Processors

- DesignWare Subsystems

- **Product L2**: (select the name that best matches your product)

- d. After creating the case, attach any debug files you created.

For general usage information, refer to the following article in SolvNetPlus:

https://solvnetplus.synopsys.com/s/article/SolvNetPlus-Usage-Help-Resources

- Or, send an e-mail message to support\_center@synopsys.com (your email is queued and then, on a first-come, first-served basis, manually routed to the correct support engineer):

- Include the full product name and version number in your e-mail so it can be routed correctly.

- For simulation issues, include the timestamp of any signals or locations in waveforms that are not understood.

- Attach any debug files you created.

- Or, telephone your local support center:

- North America:

Call 1-800-245-8005 from 7 AM to 5:30 PM Pacific time, Monday through Friday.

All other countries: https://www.synopsys.com/support/global-support-centers.html

# 2.1 Package Content

The DesignWare ARC HS4xD Development Kit package contains the following items:

- DesignWare ARC HS4xD Development Kit (herein referred to as ARC HSDK-4xD in this document)

- A 100-240 V AC power adapter (including adapters for U.S., UK, and EU outlets)

- USB cable

#### Warning

The DesignWare ARC HS4xD Development Kit contain static-sensitive devices.

# 2.2 Getting Started

This section includes instructions for the following tasks:

- 1. Installing device drivers

- 2. Checking default board settings

- 3. Installing and configuring PuTTY

- 4. Starting U-Boot

## 2.2.1 Installing Device Drivers

Before the USB-JTAG and the USB-UART interfaces can be used, you must install the required drivers on the computer where you intend to run the MetaWare debugger [5] or another serial debug console (such as PuTTY or other hyper-terminals).

The driver is a part of the Digilent Adept tool. You can download the most recent version of the Digilent Adept tool from the Digilent website at <a href="http://www.digilentinc.com">http://www.digilentinc.com</a>, and follow the installation instructions provided by Digilent.

## 2.2.3 Checking Default Board Settings

Check if the boot switches and jumpers are set to their default positions.

For an overview of the configuration options and the default settings, see Configuration and Boot Modes on page 36. Connect the ARC HSDK-4xD to your PC by connecting the USB cable to the USB data port of the ARC HSDK-4xD and the PC.

Connect the power supply included in the product package to the ARC HSDK-4xD.

The ARC HSDK-4xD must be powered by an external power adapter. Also, when the ARC HSDK-4xD is mounted on a HAPS system, the board ARC HSDK requires this external power adapter.

## 2.2.4 Installing and Configuring PuTTY

PuTTY is a serial console that can be used as a simple debug console.

- Download putty.exe from http://www.putty.org

- 2. Open the Windows Control Panel.

- In the category Hardware and Sound, click View devices and printers, and Digilent Adept USB Device.

The **Digilent Adept USB Device Properties** windows opens.

Select the **Hardware** tab and note the COM port assigned to the USB Serial Port.

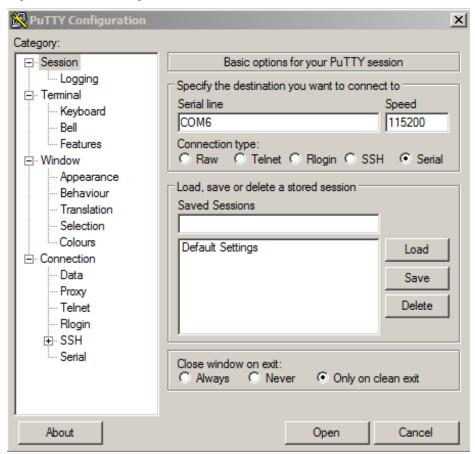

The example in Figure 1 uses the COM6 port:

Figure 1 Identification of COM Port

4. Execute putty.exe.

## The **PuTTY Configuration** window appears.

- 5. Set the Connection type to Serial.

- 6. Enter the name of the COM port in the **Serial line** field.

- 7. Set the **Speed** field to **115200** as shown in Figure 2.

Figure 2 PuTTY Configuration

8. Click **Open** to launch the PuTTY terminal.

## 2.2.5 Starting U-Boot

By default, you press the start button on the HSDK-4xD for the ARC HS core to start executing the bootloader. After you press the start button, you see text like the following figures:

- Figure 3 shows a log from default booting, followed by U-Boot commands to initialize the HSDK-4xD board in single HS47D mode and start an application called app.bin that resides on the SD card.

- Figure 4 shows a log from default booting followed by U-Boot commands to initialize the HSDK-4xD board in HS48x4 mode and start Linux from an image on the SD card (uImage).

Figure 3 Application Boot with ARC HS47D Initialization

```

Putty

Synopsys, Inc.

ARC HS Development Kit

** IC revision: Rev 2.0

** Bootloader verbosity: Normal

** Starting HS Core 1

** HS Core running @ 500 MHz

fptr = 8** HS Core fetching application from SPI flash

** HS Core starting application

<debug uart>

U-Boot 2020.01-00017-g862d528623a (Mar 25 2020 - 13:27:20 +0300)

CPU:

ARC HS v4.0 at 500 MHz

Model: snps, hsdk-4xd

Board: Synopsys ARC HS4x/4xD Development Kit

DRAM: 1 GiB

Relocation Offset is: 3ef8b000

MMC: mmc0@f000a000: 0

Loading Environment from FAT... OK

serial0@f0005000

In:

Out:

serial0@f0005000

Err:

serial0@f0005000

Clock values are saved to environment

Warning: ethernet@f0008000 (eth0) using random MAC address - 5e:df:01:a9:c3:9a

eth0: ethernet@f0008000

hsdk-4xd# run hsdk hs47d

hsdk-4xd# hsdk_init

CPU start mask is 0xl

hsdk-4xd# fatload mmc 0:1 0x80000000 app.bin

79312 bytes read in 13 ms (5.8 MiB/s)

hsdk-4xd# setenv core entry 0 0x80000200

hsdk-4xd# hsdk_go

** selftest - Application **

Mar 24 2020

10:17:22

IC revision (dd-mm-yyyy): 6-2-2019, Time (hh:mm): 14:2

Core: ARCHS47Dx4 1

Operating mode = OP MODE SLOW DDR 333:

ARC clock freq

= 500 MHz

- ARC-AXI clock divider = 1

- AXI clock freq = 400 MHz

- DDR clock freq

= 333 MHz

- TUN clock freq

= 49 MHz

- HDMI clock freq

= 27 MHz

application finished

```

Figure 4 Linux Boot with ARC HS48x4 Initialization

```

COM19 - PuTTY

Synopsys, Inc.

ARC HS Development Kit **

** IC revision: Rev 2.0

** Bootloader verbosity: Normal

** Starting HS Core 1

** HS Core running @ 500 MHz

fptr = 8** HS Core fetching application from SPI flash

* HS Core starting application

<debug_uart>

U-Boot 2020.01-00017-g862d528623a (Mar 25 2020 - 13:27:20 +0300)

CPU: ARC HS v4.0 at 500 MHz

Model: snps, hsdk-4xd

Board: Synopsys ARC HS4x/4xD Development Kit

DRAM: 1 GiB

Relocation Offset is: 3ef8b000

mmc0@f000a000: 0

Loading Environment from FAT... OK

In:

serial0@f0005000

Out: serial0@f0005000

Err:

serial0@f0005000

Clock values are saved to environment

Warning: ethernet@f0008000 (eth0) using random MAC address - c2:15:73:94:aa:8d

eth0: ethernet@f0008000

hsdk-4xd# run hsdk_hs48x4

hsdk-4xd# hsdk init

CPU start mask is 0xf

hsdk-4xd# hsdk_clock set cpu_freq 1000 axi_freq 800 tun_freq 150

Set clocks to values specified in args

hsdk-4xd# hsdk_clock print

HSDK: clock 'cpu-clk' rate 1000 MHz

HSDK: clock 'tun-clk' rate 150 MHz

HSDK: clock 'axi-clk' rate 800 MHz

HSDK: clock 'ddr-clk' rate 334 MHz

hsdk-4xd# fatload mmc 0:1 0x82000000 uImage

22073325 bytes read in 4137 ms (5.1 MiB/s)

hsdk-4xd# setenv loadaddr 0x82000000

hsdk-4xd# bootm

## Booting kernel from Legacy Image at 82000000 ...

Image Name: Linux-5.4.0-00023-gac57d0971774-

Image Type: ARC Linux Kernel Image (gzip compressed)

Data Size:

22073261 Bytes = 21.1 MiB

Load Address: 90000000

Entry Point: 910cc000

Verifying Checksum ... OK

Uncompressing Kernel Image

CPU start mask is 0xf

Starting kernel ...

```

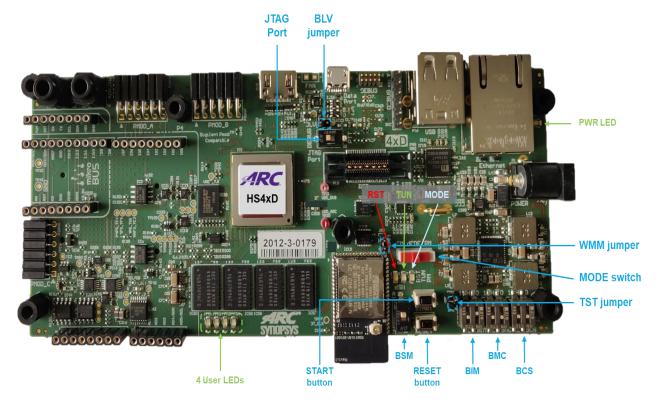

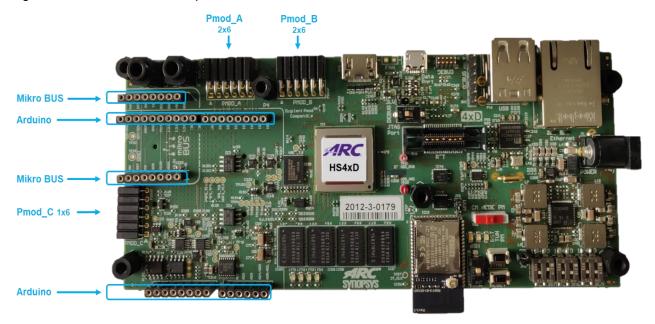

# 2.3 Location of Components On HSDK-4xD

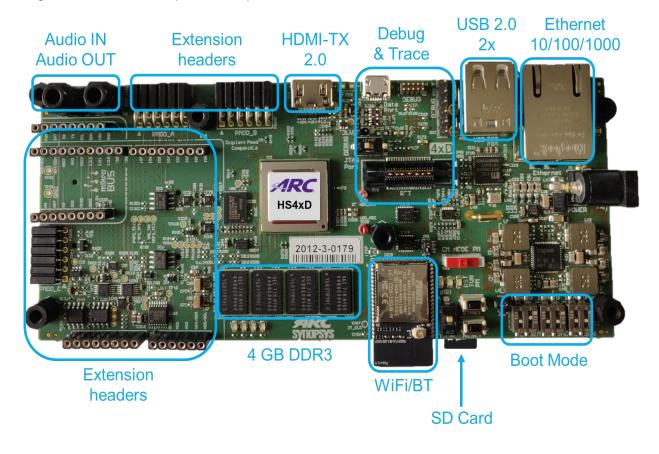

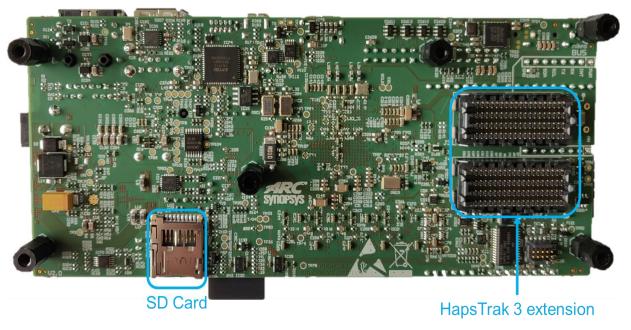

Figure 5 and Figure 6 show the placement of various components on the HSDK-4xD board.

Synopsys, Inc.

Figure 5 HSDK-4xD Components- Top View

Figure 6 HSDK-4xD Components: Bottom View

# 2.4 Software Packages

See the <a href="http://embarc.org/">http://embarc.org/</a> portal for information on the available software packages for the ARC HSDK-4xD.

Direct links to the software release is available here:

- Linux software release for ARC HSDK-4xD are available here:

https://github.com/foss-for-synopsys-dwc-arc-processors/buildroot/releases

- embARC software releases for ARC HSDK-4xD are available here:

https://github.com/foss-for-synopsys-dwc-arc-processors/embarc\_osp/releases

Additional documentation on how to get started can be found here: https://github.com/foss-for-synopsys-dwc-arc-processors/ARC-Development-Systems-Forum/wiki/ARC-Development-Systems-Forum-Wiki-Home#arc-hs-development-kit-1

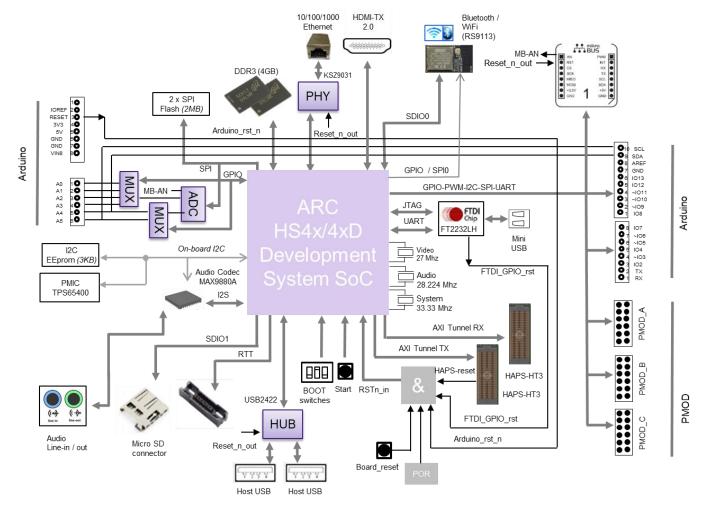

## 3.1 Overview of ARC HSDK-4xD

Figure 7 ARC HSDK-4xD Block Diagram

DesignWare ARC HS4xD Development Kit contains the following components:

- ARC HS4xD Development System SoC

- Quad Core ARC HS4x/4xD

- DDR3 memory interface

- GPU

- USB, Ethernet, SDIO

- Several APB Peripherals

#### Memory

- o DDR3-1333 (4 GB)

- o NOR Flash (1 MB)

- o 2x SPI Flash (2 MB)

- o I2C EEPROM (3 KB)

#### Interfaces

- o HDMI-TX 2.0

- USB2 (2x)

- o Ethernet (10/100/1000)

- o Audio line in/out

- USB Data port (JTAG/UART)

- Micro-SD Card

- o WiFi/Bluetooth module

- o ADC (6 channels)

- o RTT Nexus, JTAG

#### Extensions

- o AXI Tunnel (32-bit, max 150 MHz)

- o Arduino Interface headers (UNO R3 compatible)

- o mikroBUS headers

- Pmod Interfaces (3x)

I2S RX

reset

# 3.2 Overview of ARC HS4xD Development System SoC

RTT JTAG DDR3 TUNNEL USB2.0 RGMII EBI SD v2.0 HDMI 1333Mbps 150MHz 480Mbps 125MHz SDIO 50MHz 2.0 mux HS4xD-3 HS4xD-1 MMU MMU ICACHE DCACHE ICACHE DCACHE PHY PHY PHY 2x SDIO 50MH z Real-Time-Trace 60MHz HS4xD-2 HS4xD-4 **HDMI** DCCM DCACHE MCTL SDIO AXI SDIO **USB ETH** EBI **PGU** tunnel 512KB L2 cache DMI BIU 64bit AXI AXI2APB AXI2APB 32kB 256kB GPU DMA ROM **SRAM** 1x 1x DEBUG 2x 2x 3x GPIO WDT CGU CREG I2C SPI UART I2C SPI UART RTC TIMERS mux UART PMOD I2C SPI clk boot I2S TX &

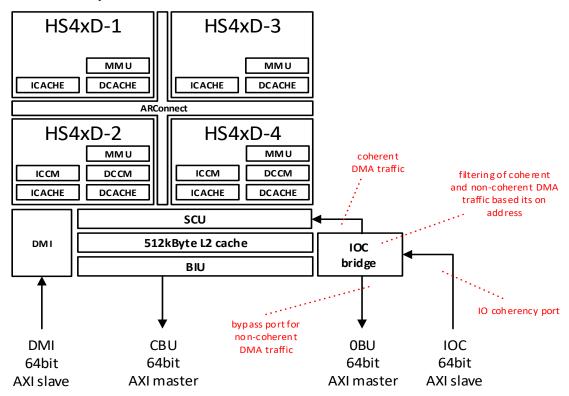

Figure 8 ARC HS4xD Development System SoC Top-Level Diagram

The ARC HS4xD Development System SoC provides the following main features:

- Flexible, customizable IC architecture

- Configurable/programmable boot scenarios

- Configurable/programmable memory map

- DesignWare ARC HS4xD quad-core @ 1GHz

- o 64 KB instruction cache

- 64 KB data cache

- 256 KB ICCM (two cores)

- 256 KB DCCM (two cores)

- Memory Management Unit

- Physical Address Extension (PAE)

- 256 KB Cluster Shared Memory

- 512 KB L2 cache

- Support for I/O coherency

- Support for ARC Real-Time Trace

- Think Silicon NemaT Graphics Processing Unit @ 400 MHz

- Flexible clock generation

- System locks

- 33 MHz system reference clock input

- PLL for DDR clock

- PLL for TUNNEL clock

- PLL for ARC clock

- PLL for all other system clocks

- Audio

- Audio reference clock input (24.576 MHz)

- Integer divider(s) for audio serial clock

- 256 KB SRAM

- DDR3 interface

- Maximum speed grade DDR-1333 (400 MHz)

- o 32-bit data width

- Maximum row address width of 16-bits

- Maximum bank address width: 3-bits

- Maximum two memory ranks

- Maximum supported DDR memory size is 4 GB

- I2S TX/RX interface

- USB 2.0 Host interface

- SD card interface

- SDIO interfaces

- 10/100/1000Mbps Ethernet RGMII interface

- AXI tunnel interface

- Source-synchronous

- Maximum frequency of 150 MHz

- Maximum data throughput of 600 MB per second

- UART interfaces

- I2C interfaces

- SPI interfaces

- PWM interfaces

- JTAG interface

## 3.3 Clocks and Resets

## 3.3.1 Clocks

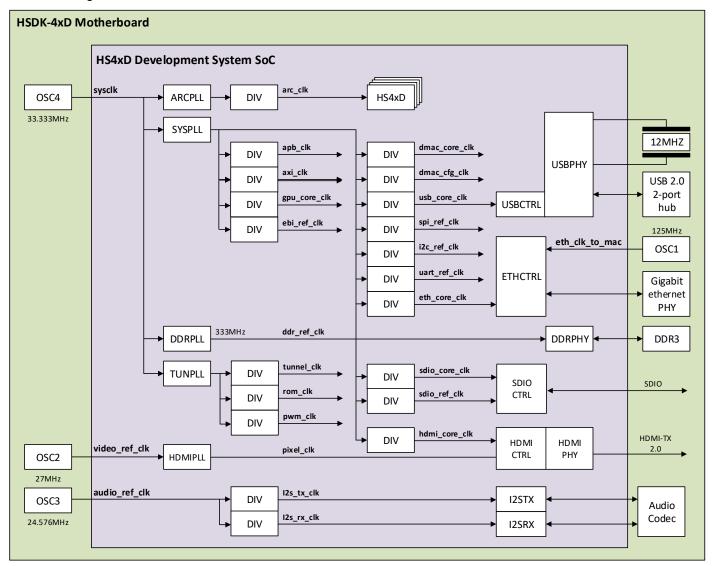

The ARC HS4xD Development System SoC uses a single 33 MHz reference clock from which all the system clocks are generated. The clock generation is centralized in the Clock Generation Unit (CGU). The CGU implements several PLLs and integer dividers that allow for accurate fine-tuning of the system clocks to the desired frequency. For more details on the CGU, see Clock Registers on page 86. Figure 9 shows the HSDK-4xD clock architecture.

Figure 9 ARC HSDK-4xD Clock Architecture

Table 1 lists the summary of all the clocks and their sources.

Table 1 Overview of ARC HSDK-4xD Clock Components

| HS IC Clock   | Clock Source | Value After<br>U-Boot | Description                                                      |

|---------------|--------------|-----------------------|------------------------------------------------------------------|

| arc_clk       | sysclk       | 500                   | Clock for ARC HS4xD quad-core (including ARC RTT and ARConnect)  |

| apb_clk       | sysclk       | 200                   | Clock for APB peripherals                                        |

| axi_clk       | sysclk       | 400                   | Clock for AXI network                                            |

| eth_core_clk  | sysclk       | 400                   | Core clock for Ethernet MAC                                      |

| usb_core_clk  | sysclk       | 400                   | Core clock for USB-HOST controller                               |

| sdio_core_clk | sysclk       | 400                   | Core clock for SDIO controller                                   |

| hdmi_core_clk | sysclk       | 400                   | Core clock HMDI                                                  |

| gpu_core_clk  | sysclk       | 400                   | Core clock GPU                                                   |

| dmac_core_clk | sysclk       | 400                   | Core clock for DMAC                                              |

| dmac_cfg_clk  | sysclk       | 200                   | Configuration clock for DMAC                                     |

| sdio_ref_clk  | sysclk       | 100                   | Reference clock for SD card interface                            |

| spi_ref_clk   | sysclk       | 33.33                 | Reference clock for SPI baud rate.                               |

|               |              |                       | SPI reference clock must be less than or equal to the APB clock. |

| i2c_ref_clk   | sysclk       | 200                   | Reference clock for I2C baud rate.                               |

| HS IC Clock   | Clock Source  | Value After<br>U-Boot | Description                                                                                                                                                      |

|---------------|---------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |               |                       | I2C reference clock must be greater than or equal to the APB clock                                                                                               |

| uart_ref_clk  | sysclk        | 33.33                 | Reference clock for UART baud rate.  UART reference clock must be less than or equal to APB clock                                                                |

| ddr_ref_clk   | sysclk        | 333                   | Reference clock for DDR controller + PHY (333 MHz for DDR-1333). This clock is driven directly by the PLL; all the integer dividers inside the CGU are bypassed. |

| tunnel_clk    | sysclk        | 50                    | Clock for AXI tunnel                                                                                                                                             |

| rom_clk       | sysclk        | 150                   | Clock for ROM controller                                                                                                                                         |

| pwm_clk       | sysclk        | 75                    | Clock for PWM controller                                                                                                                                         |

| timer_clk     | sysclk        | 50                    | Clock for TIMERS / RTC                                                                                                                                           |

| i2s_tx_sclk   | audio_ref_clk | 24.576                | Audio serial clock for Tx channel                                                                                                                                |

| i2s_rx_sclk   | audio_ref_clk | 24.576                | Audio serial clock for Rx channel                                                                                                                                |

| eth_clk       | osc1          | 125                   | Fixed clock for Ethernet MAC                                                                                                                                     |

| video_ref_clk | osc2          | 27                    | Fixed clock for PGU and HDMI                                                                                                                                     |

| audio_ref_clk | osc3          | 24.576                | Fixed clock frequency for I2S interfaces and audio codec                                                                                                         |

| sysclk        | OSC4          | 33.333                | Fixed system clock for ARC HS4xD Development System SoC                                                                                                          |

#### 3.3.2 **Reset**

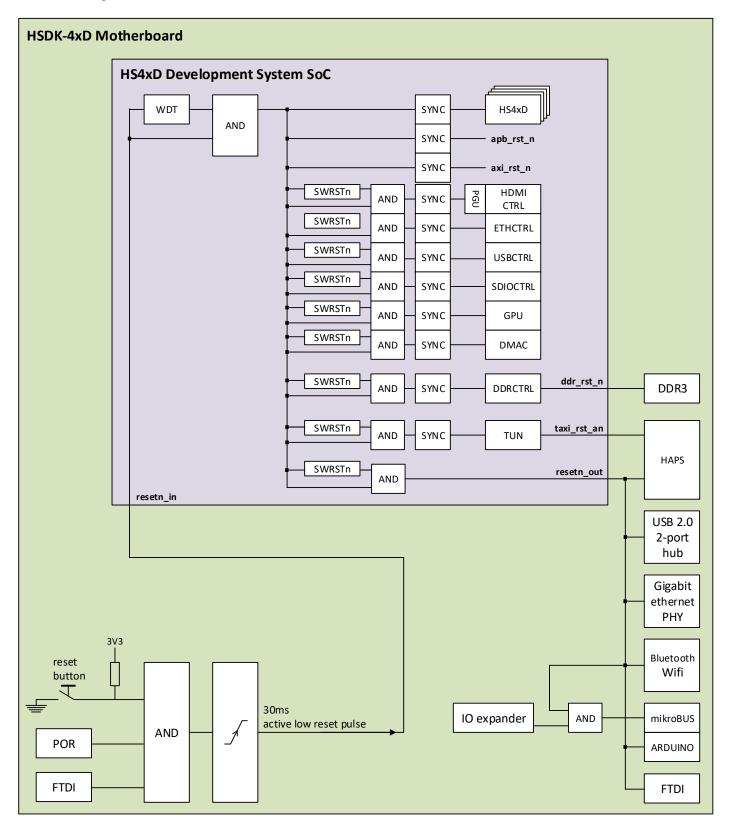

Figure 10 shows the top-level reset architecture of the ARC HSDK-4xD.

When the ARC HS4xD Development System SoC is in reset the resetn\_out is asserted. This output pin resets all components on the board that have a reset input pin (for example: Gigabit Ethernet PHY, USB 2.0 2-port hub, and so on).

The ARC HS4xD Development System SoC has one external reset pin (resetn\_in) that serves as an active low, hardware reset. When the external hardware reset is active, the entire chip is reset. The chip does not have an on-chip power-on-reset module so it relies on the external circuitry to keep resetn\_in asserted low until all the chip power supplies and the system input clock are stabilized.

The reset generated by the reset button is merged with a Power on Reset circuit and the FTDI\_gpio reset.

After the ARC HS4xD Development System SoC is out of reset, resetn\_out is asserted resetting all the HSDK-4xD components, resetn\_out is also routed to the mikrobus and Arduino headers and to the HapsTrak 3 connector. The reset input of the Mikrobus/Click shield is asserted by resetn\_out but can also be asserted through a software-controllable GPIO output from the on board I2C I/O expander.

Further, an AXI tunnel reset signal taxi\_rst\_an is available on the HapsTrak 3 connector. This signal allows you to reset the AXI tunnel on the HAPS side independently from the ARC HS4xD Development System SoC reset.

Figure 10 ARC HSDK-4xD Reset Architecture

# 3.4 Interrupts

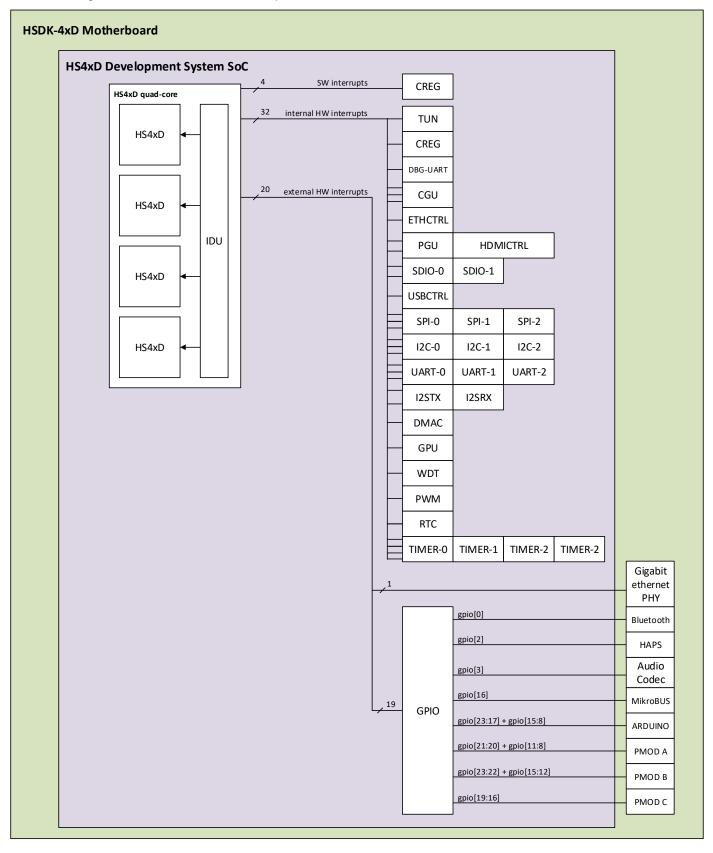

Figure 11 shows the top-level interrupt architecture of the ARC HSDK-4xD. The ARC HSDK-4xD distinguishes between the following three interrupt sources:

- Software (SW) interrupts: a software interrupt can be generated by writing a 1 to the corresponding interrupt bit in the in the CREG module.

- External hardware interrupts: generated by off-chip interrupt sources (for example: external host CPU). The interrupt requests are received by the GPIO module and forwarded to the ARC HS4xD quad-core.

- Internal hardware interrupts: generated by the on-chip interrupt sources (for example: I2C, UART, SPI).

Table 2 lists the The interrupt mapping for the ARC HS4xD quad-core. All the above motioned interrupts sources are connected as an external common interrupt to the interrupt distribution unit (IDU). The IDU distributes the external common interrupts to the cores in the ARC HS4xD quad-core. All interrupts are active high and level sensitive unless noted differently.

Figure 11 ARC HSDK-4xD Interrupt Architecture

Table 2 ARC HSDK-4xD Interrupt Mapping

| IRQ#    |             | Interrupt Source                   | Remarks                                        |

|---------|-------------|------------------------------------|------------------------------------------------|

| IDU     | CORE        |                                    |                                                |

|         | •           | ARC Internal Inte                  | rrupts                                         |

|         | irq0        | reset                              |                                                |

|         | irq1        | memory error                       |                                                |

|         | irq2        | instruction error                  |                                                |

|         | irq16       | timer0                             |                                                |

|         | irq17       | timer1                             |                                                |

|         | ·           | ARC External Private               | Interrupts                                     |

|         | irq18_a     | reserved                           |                                                |

|         | irq19_a     | ARConnect inter-core interrupt     |                                                |

|         | irq20_a     | reserved                           |                                                |

|         | irq21_a     | reserved                           |                                                |

|         | irq22_a     | reserved                           |                                                |

|         | irq23_a     | reserved                           |                                                |

| ARC     | External Co | ommon Interrupts (Rout             | ed through ARConnect IDU)                      |

| cirq0_a | irq24_a     | SW interrupt from CREG INT bit [0] |                                                |

| cirq1_a | irq25_a     | SW interrupt from CREG INT bit [1] |                                                |

| cirq2_a | irq26_a     | SW interrupt from CREG INT bit [2] |                                                |

| cirq3_a | irq27_a     | SW interrupt from CREG INT bit [3] |                                                |

| cirq4_a | irq28_a     | internal HW interrupt from TUNNEL  | Parity error                                   |

| cirq5_a | irq29_a     | internal HW interrupt from CREG    | Address decoder updated; <b>edge</b> sensitive |

| cirq6_a  | irq30_a | internal HW interrupt from DEBUG-UART  |                                |

|----------|---------|----------------------------------------|--------------------------------|

| cirq7_a  | irq31_a | internal HW interrupt from CGU         | PLL locked; edge sensitive     |

| cirq8_a  | irq32_a | internal HW interrupt from CGU         | PLL unlocked; edge sensitive   |

| cirq9_a  | irq33_a | internal HW interrupt from CGU         | PLL lock error; edge sensitive |

| cirq10_a | irq34_a | internal HW interrupt from ETH MAC     |                                |

| cirq11_a | irq35_a | external HW interrupt from ETH PHY     |                                |

| cirq12_a | irq36_a | internal HW interrupt<br>from SDIO0    |                                |

| cirq13_a | irq37_a | internal HW interrupt from PGU         |                                |

| cirq14_a | irq38_a | internal HW interrupt from HDMI        |                                |

| cirq15_a | irq39_a | internal HW interrupt<br>from USB-HOST |                                |

| cirq16_a | irq40_a | internal HW interrupt<br>from SPI0     |                                |

| cirq17_a | irq41_a | internal HW interrupt<br>from SPI1     |                                |

| cirq18_a | irq42_a | internal HW interrupt<br>from SPI-2    |                                |

| cirq19_a | irq43_a | internal HW interrupt<br>from I2C0     |                                |

| cirq20_a | irq44_a | internal HW interrupt<br>from I2C1     |                                |

| cirq21_a | irq45_a | internal HW interrupt<br>from I2C2     |                                |

| cirq22_a | irq46_a | internal HW interrupt from UART0       |                                |

| cirq23_a | irq47_a | internal HW interrupt from UART1       |                                |

| cirq24_a i | irq48_a | internal HW interrupt from UART2     |                                          |

|------------|---------|--------------------------------------|------------------------------------------|

| cirq25_a i | irq49_a | internal HW interrupt<br>from I2S-TX |                                          |

| cirq26_a i | irq50_a | internal HW interrupt<br>from I2S-RX |                                          |

| cirq27_a i | irq51_a | internal HW interrupt from DMAC      |                                          |

| cirq28_a i | irq52_a | internal HW interrupt from GPU       |                                          |

| cirq29_a i | irq53_a | internal HW interrupt<br>from WDT    |                                          |

| cirq30_a i | irq54_a | internal HW interrupt from PWM       |                                          |

| cirq31_a i | irq55_a | reserved                             |                                          |

| cirq56_a i | irq80_a | internal HW interrupt from SDIO1     |                                          |

| cirq57_a i | irq81_a | internal HW interrupt from TIMER1    |                                          |

| cirq58_a i | irq82_a | internal HW interrupt<br>from TIMER2 |                                          |

| cirq59_a i | irq83_a | internal HW interrupt from TIMER3    |                                          |

| cirq60_a i | irq84_a | internal HW interrupt<br>from TIMER4 |                                          |

| cirq61_a i | irq85_a | internal HW interrupt from RTC       |                                          |

| cirq32_a i | irq56_a | external HW interrupt from GPIO[0]   | Bluetooth interrupt of RS9113 module     |

| cirq33_a i | irq57_a | reserved                             | N/A, GPIO[1] is used as output           |

| cirq34_a i | irq58_a | external HW interrupt from GPIO[2]   | HAPS interrupt (on HapsTrak 3 connector) |

| cirq35_a i | irq59_a | external HW interrupt from GPIO[3]   | Audio codec (MAX9880A)<br>interrupt      |

| cirq36_a i | irq60_a | reserved                             | N/A, GPIO[4] is not connected            |

|          | 1       | T                                   | T                                       |

|----------|---------|-------------------------------------|-----------------------------------------|

| cirq37_a | irq61_a | reserved                            | N/A, GPIO[5] is not connected           |

| cirq38_a | irq62_a | reserved                            | N/A, GPIO[6] is not connected           |

| cirq39_a | irq63_a | reserved                            | N/A, GPIO[7] is not connected           |

| cirq40_a | irq64_a | external HW interrupt from GPIO[8]  | Available on Arduino and PMOD_A header  |

| cirq41_a | irq65_a | external HW interrupt from GPIO[9]  | Used on Arduino and PMOD_A header       |

| cirq42_a | irq66_a | external HW interrupt from GPIO[10] | Available on Arduino and PMOD_A header  |

| cirq43_a | irq67_a | external HW interrupt from GPIO[11] | Available on Arduino and PMOD_A header  |

| cirq44_a | irq68_a | external HW interrupt from GPIO[12] | Available on Arduino and PMOD_B header  |

| cirq45_a | irq69_a | external HW interrupt from GPIO[13] | Available on Arduino and PMOD_B header  |

| cirq46_a | irq70_a | external HW interrupt from GPIO[14] | Available on Arduino and PMOD_B header  |

| cirq47_a | irq71_a | external HW interrupt from GPIO[15] | Available on Arduino and PMOD_B header  |

| cirq48_a | irq72_a | external HW interrupt from GPIO[16] | Available on MikroBUS and PMOD_C header |

| cirq49_a | irq73_a | external HW interrupt from GPIO[17] | Available on Arduino and PMOD_C header  |

| cirq50_a | irq74_a | external HW interrupt from GPIO[18] | Available on Arduino and PMOD_C header  |

| cirq51_a | irq75_a | external HW interrupt from GPIO[19] | Available on Arduino and PMOD_C header  |

| cirq52_a | irq76_a | external HW interrupt from GPIO[20] | Available on Arduino and PMOD_A header  |

| cirq53_a | irq77_a | external HW interrupt from GPIO[21] | Available on Arduino and PMOD_A header  |

| cirq54_a | irq78_a | external HW interrupt from GPIO[22] | Available on Arduino and PMOD_B header  |

| cirq55_a | irq79_a | external HW interrupt from GPIO[23] | Available on Arduino and PMOD_B header  |

| cirq62_a | irq80_a | reserved |  |

|----------|---------|----------|--|

| cirq63_a | irq81_a | reserved |  |

# 3.5 Debug and Trace

The HSDK-4xD offers a rich set of debug and trace options:

#### Debug:

- USB cable connected to on-board 2-channel FTDI chip

- Compatible with MetaWare debugger and GDB

- Ashling Opella-XD, Lauterbach Trace-32, Digilent HS1 and 2 support through:

- o A 10-pin 5 mil debug header and an adapter cable

- A 6-pin 10 mil debug header and flying leads

#### Trace:

- Both on-chip through DDR or off-chip through the Nexus interface into external host trace off-load is available

- Ashling Ultra-XD and Lauterbach Trace-32 are supported.

Figure 12 shows the various debug and trace headers.

JTAG port switch

Nexus Mictor 38

Figure 12 ARC HSDK-4xD Debug and Trace Headers

## 3.5.1 **Debug**

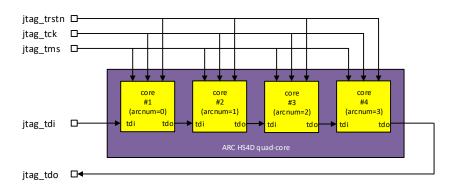

The HSDK-4xD provides debug access through an IEEE 1149.1 JTAG port. The four ARC HS cores in the ARC HS4xD quad-core cluster are daisy-chained into a JTAG chain. In a JTAG chain, the data output from the first core becomes the data input to the second core and so forth; the control and clock signals are common to all the cores in the chain. The JTAG chain for the ARC HS4xD Development System SoC is shown in Figure 13. To distinguish between the individual cores in the JTAG chain each core has a unique JTAG IDCODE.

Figure 13 JTAG Daisy Chain

Table 3 ARC ID Codes

| Core         | ARC ID | CPUNUM in MDB |

|--------------|--------|---------------|

| ARC HS4xD #1 | 0x054  | 1             |

| ARC HS4xD #2 | 0x154  | 2             |

| ARC HS4xD #3 | 0x254  | 3             |

| ARC HS4xD #4 | 0x354  | 4             |

## 3.5.1.1 USB Dataport

The USB Dataport can be connected to your PC using the USB cable included in the product package. A USB converter from FTDI (FT2232HL) converts one channel to a serial communication protocol (UART). The other channel is converted to JTAG.

The JTAG channel offered over this Dataport is compatible with the MetaWare debugger. The serial communication channel is used as console and can be monitored using a standard hyper terminal application for example: PuTTY. For more information, see Getting Started.

#### 3.5.1.2 10-Pin Header Pinout

This header can be used to connect a standard 20-pin Ashling or Lauterbach probe header using an adapter as depicted below

Figure 14 10-Pin to 20-Pin JTAG Adapter

The company Embedded Artists offers such a 10-pin to 20-pin JTAG Adapter.

Article code: EA-ACC-040. The adapter can be purchased from many known distributors such as Mouser, Digikey, and so on.

## 3.5.1.3 6-Pin Header Pinout

This 6-pin header is compatible with the standard Digilent HS1 and HS2 probes.

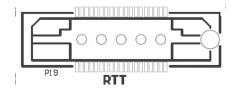

## 3.5.2 ARC Real-Time Trace

The ARC HS4xD Development System SoC implements Real-Time-Trace capability (ARC RTT). ARC RTT allows configurable/programmable monitoring of:

- Program flow and instruction execution

- Data reads and writes

- Auxiliary reads and writes

- Core register writes

Trace data can either be off-loaded from internal ARC RTT buffers to an on-chip memory (that is, DDR), or to an off-chip memory in an external host using the Nexus 5001 interface.

The Nexus 5001 interface is a 16-bit high-speed interface and for the ARC HS4xD Development System SoC supports up to 100 MHz trace clock.

## 3.5.2.1 Nexus Mictor 38 Interface

The ARC RTT interface is supported with the Ashling Ultra-XD and Lauterbach Trace-32 products.

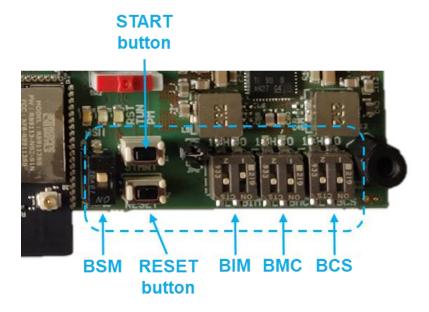

# 3.6 Configuration and Boot Modes

Figure 15 depicts the configuration switches, jumpers, and LEDs available on the HSDK-4xD. Besides jumpers and standard Reset and Start buttons there are also switches to control the board boot mode and debug mode. More detail of each of the jumpers and switches are explained in the following sections.

Figure 15 ARC HSDK-4xD Configuration and Boot Switches and Buttons

#### 3.6.1 Boot Switches

Figure 16 ARC HSDK-4xD Boot Switches

### **Boot Image location (BIM) Switches**

Ensure that these switches are set as depicted on the left (**default position**). This setting ensures that the pre-bootloader starts executing the U-Boot bootloader that is stored in SPI Flash. All other settings for these switches are reserved and must not be used.

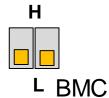

#### **Boot Multi -Core (BMC) Switches**

These switches are all reserved. The setting of these switches is currently not used by the pre-bootloader. Note that selecting multi-core operating modes can be controlled directly from the U-Boot bootloader.

### Boot Core Select (BCS) switches.

Ensure that these switches are set as depicted on the left (**default position**). This setting ensures that the ARC HS4xD core 1 starts executing U-Boot. All other settings for these switches are reserved and not be used.

### Boot Start Mode (BSM) switch.

This switch controls manual or automatic booting of the ARC HSDK-4xD:

*Manual* mode. The HSDK-4xD only starts booting after the *START* button is pushed. This is the **default setting**

Automatic mode. The HSDK-4xD automatically starts booting after Reset.

### 3.6.2 Jumpers

The HSDK-4xD includes the following jumpers: TST, BLV, and WMM.

The TST jumper (JP8) is used for production purposes only and must not be used in the normal course of operation. **Default position**: open

The WMM jumper (Wireless Module Mode) is used to control the mode of the RS9113 Wireless Module. If the jumper is *closed,* the module is set to operate in the hosted mode using the SDIO interface. In this mode, the networking stacks are running on the ARC HS4xD Core. If the jumper is *open,* the module operates in the embedded mode using the SPI interface,and hence the full networking stack is running on the RS9113 module itself.

**Default position**: closed

The BLV jumper (Boot Loader Verbosity) is used to control the verbosity of the bootloader messages. If the jumper is *open*, the boot loader prints the normal boot messages without additional system/debug info. If the jumper is closed, the boot loader prints additional messages during execution.

**Default position**: open

#### 3.6.3 Other Switches

Besides the bootmode switches, the HSDK-4xD includes the following switches:

**JTAG-port switch**: This switch is used to control how the JTAG signals are routed. If the switch is in the on postion (left), the JTAG signals are available on the 6-pin and 10-pin debug headers as well as through the USB Dataport. If the switch is in the off position (right), the JTAG signals are avialable on the ARC RTT connector. **Default position:** on.

**MODE switch**: This switch is used to select the operating mode of the HSDK-4xD. Currently only the *Core Mode*; switch in CM position is supported. **Default position**: CM

#### 3.6.4 On-board LEDs

The HSDK-4xD includes the following LEDs: 4 user LEDs and 4 status/system LEDs. Table 4 summarizes the status/system LEDs. The user LEDs can be controlled through the I/O expander using the on-board I2C bus (see sections: On-board I2C Control Bus and I/O Expander).

Table 4 ARC HSDK-4xD Status and System LEDs

| LED | Color | Description                                                                                                                              |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| RST | red   | Reset LED, this LED turns red if the ARC HSDK-4xD is in Reset.                                                                           |

| TUN | green | Tunnel BIST, indicates that the AXI Tunnel self-test is OK after connecting HSDK-4xD on a HAPS system through the HapsTrak 3 connectors. |

| РМ  | blue  | The HSDK-4xD is in Peripheral MODE. This mode is currently not available.                                                                |

| PWR | green | Indicates that the power supplies for the HSDK-4xD are OK.                                                                               |

# 3.7 Memories

The HSDK-4xD features the following memories

- 4 GB DDR3-1333 memory

- 2 MB SPI Flash

- This SPI Flash is pre-loaded with the U-Boot bootloader

- 3 KB I2C EEprom

### 3.8 USB Interface

The HSDK-4xD offers two USB 2.0 host ports. The ARC HS4xD Development System SoC includes a single DesignWare USB 2.0 host controller and PHY and through an onboard USB Hub (USB2422) two USB ports are available. The controller supports high-speed (480 Mbps) transfers using an EHCI Host Controller, as well as full (12 Mbps) and low (1.5 Mbps) speeds through the integrated OHCI Host Controller. See references [11] and [12] for more info on the USB Host controller and PHY.

### 3.9 Ethernet Interface

On the HSDK-4xD, Ethernet access is provided through a combination of the Synopsys DesignWare Ethernet MAC [10] and an external KSZ9031 triple-speed Ethernet Physical Layer from Microchip and supports the supports the 10/100/1000 Mbps link speeds. The PHY is connected to the ARC HS4xD Development System SoC using the RGMII interface. An RJ45 connector with LED indicators is used as external interface.

On the RJ45 connector, only the LED on the left side is used and this LED indicates the link speed, see Table 5. The LED on the right side is not connected.

Table 5 Ethernet Link Speed Indication

| Link Speed | Color  |

|------------|--------|

| 10 Mbps    | Yellow |

| 100 Mbps   | Orange |

| 1000 Mbps  | Green  |

# 3.10 SD Card Interface

The HSDK-4xD features a micro SD-card interface supporting the following micro SD cards:

- SD (SDSC)

- SDIO (Secure Digital Input Output)

- SDHC (The Secure Digital High Capacity, capacities up to 32 GB)

- SDXC (The Secure Digital Extended Capacity, supports cards up to 2 TB)

After U-Boot, the default settings operate the SD card in the SDR25 speed mode. The micro SD-card interface is controlled by SDIO0 controller.

# 3.11 Redpine® WiFi / Bluetooth Interface

The HSDK-4xD includes the Redpine® Signals RS9113 module for communication using Wi-Fi, Bluetooth, and Zigbee. For more information, see *Redpine Signals RS9113-WiseConnect-API-Guide-v1.7.1* in References.

The SDIO host interface of the Redpine® Signals RS9113 module is connected to the SDIO1 controller. The SPI host interface is connected to the SPI0 controller. The operating mode of the RS9113 module is controlled by the WMM jumper, see Jumpers for details. By default, the RS9113 is set in SDIO host interface mode.

# 3.12 Audio Interface

The ARC HSDK-4xD board features stereo audio jacks for Line Out and Line In. The stereo audio input and output signals are converted using a MAX9880A stereo codecs from Maxim Integrated, which provides the interface between the stereo I<sup>2</sup>S [17] ports of the ARC HS4xD Development System SoC and drives the Line Out and Line In interfaces.

The I<sup>2</sup>S ports operate in master mode, which means that the I<sup>2</sup>S IPs inside the ARC HS4xD Development System SoC initialize and drive the I<sup>2</sup>S word select and serial clock signal. The I<sup>2</sup>S serial clocks are generated by integer dividers that run at a fixed audio reference clock frequency of 24.576 MHz.

The HSDK-4xD supports the following sampling frequencies: 16 kHz, 32 kHz, 48 kHz, 96 kHz, and 192 kHz. I<sup>2</sup>S SCLK divider settings are shown in Table 6.

Table 6 I2S SCLK Divider Settings

| Audio Sample Rate |        |        |        |         |  |  |  |

|-------------------|--------|--------|--------|---------|--|--|--|

| 16 kHz            | 32 kHz | 48 kHz | 96 kHz | 192 kHz |  |  |  |

| 24 12 8 | 4 | 2 |

|---------|---|---|

|---------|---|---|

# 3.13 On-board I2C Control Bus

The HSDK-4xD board offers an on-board I2C bus [16] to control the following on-board devices:

- Power management IC (PMIC)

- Audio Codec

- I2C EEprom (inside I/O Expander)

- I/O Expander

An overview of the I2C bus slave addresses can be found in Table 7. The on-board I2C bus is controlled by I2C0.

Table 7 ARC HSDK-4xD On-board I2C Save Addresses

| Device Name | Description                | 7-bit I <sup>2</sup> C Address |

|-------------|----------------------------|--------------------------------|

| TPS65400    | Power Management IC (PMIC) | 1101001 = 0x69                 |

| MAX 9880A   | Audio Codec                | 0010000 = 0x10                 |

| CY8C9520A   | I/O Expander part          | 0100000 = 0x20                 |

|             | 3 KB EEprom part           | 1000000 = 0x40                 |

# 3.14 ADC

The HSDK-4xD board includes the 8-input 10-bit ADC108S102 from Texas Instruments [3]. The conversion rate ranges from 500 kSPS to 1 MSPS. The analog input range is 0 to 5 Volt. The analog input values are read using the SPI0 peripheral using SPI chip select 1. Table 8 lists the various ADC channels and their usage.

Table 8 ADC Channel Usage

| ADC IN | Usage       |

|--------|-------------|

| 0      | Arduino AD0 |

| 1      | Arduino AD1 |

| 2      | Arduino AD2 |

| 3      | Arduino AD3 |

| 4 | Arduino AD4 |

|---|-------------|

| 5 | Arduino AD5 |

| 6 | mikroBUS AN |

| 7 | not used    |

# 3.15 I/O Expander

The HSDK-4xD board includes a CY8C9520A I/O expander from Cypress [4]. The I/O expander offers additional GPIO signals and board control signals and can be accessed through the on-board I2C bus, see section On-board I2C Control Bus. Table 9 gives an overview of relevant I/O signals.

Table 9 I/O Expander I/O Overview

| Port0  | Usage                                       | Port1 | Usage               |

|--------|---------------------------------------------|-------|---------------------|

| bit0   | RS9113 Bluetooth I2S RX enable (active low) | bit03 | reserved            |

| bit1   | mikroBUS Reset (active low)                 | bit4  | On-board user LED 1 |

| bit2   | GPIO for Arduino AD0                        | bit5  | On-board user LED 2 |

| bit3   | GPIO for Arduino AD1                        | bit6  | On-board user LED 3 |

| bit4   | GPIO for Arduino AD2                        | bit7  | On-board user LED 4 |

| bit5   | GPIO for Arduino AD3                        |       |                     |

| bit6,7 | Reserved                                    |       |                     |

# 3.16 Extension Interfaces

To build your application context around the ARC HSDK-4xD, the following peripheral module standards are supported:

- Digilent Pmod<sup>™</sup> (3x)

- MikroBUS (1x)

- Arduino (1x)

Figure 17 ARC HSDK-4xD Peripheral Extension Interfaces

Additionally, the ARC HSDK-4xD features two HapsTrak 3 connectors that allow you to connect the ARC HSDK-4xD to a HAPS prototyping system. See HapsTrak3 Extension on page 51for more details regarding this extension option.

Figure 18 ARC HSDK-4xD HAPS Extension Interface

April 2020

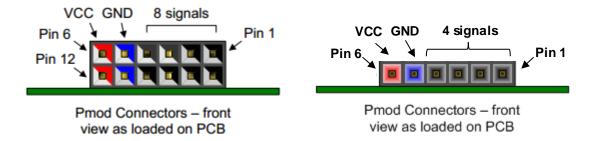

# 3.16.1 Digilent Pmod™

The HSDK-4xD features two 12-pin Pmod connectors  $Pmod_A$  and  $Pmod_B$  and one 6-pin Pmod connector  $Pmod_C$ . The functionality of the Pmod connectors is programmable and includes GPIO [6], UART [14], SPI [15], I2C [16] and PWM. The available options are summarized in Table 10. The available options are limited if the Pmod header is used in conjunction with a MikroBUS Click or Arduino shield. Multiplexing is controlled by software using the  $PMOD_MUX_CTRL$  register (see Mux ). After a reset, all ports are configured as GPIO inputs [6].

| Table 10 | Available Protocol Options |

|----------|----------------------------|

|          |                            |

|          |      | PMOD_A       |                |                  | PMOD_B       |                |                  | PMOD_C       |                |                  |

|----------|------|--------------|----------------|------------------|--------------|----------------|------------------|--------------|----------------|------------------|

|          | Mode | PMOD<br>Only | PMOD+<br>Click | PMOD+<br>Arduino | PMOD<br>Only | PMOD+<br>Click | PMOD+<br>Arduino | PMOD<br>Only | PMOD+<br>Click | PMOD+<br>Arduino |

|          | gpio | х            | х              |                  | х            | х              |                  | х            | х              | х                |

|          | uart | х            | х              | х                | х            | х              | х                | х            |                |                  |

| Protocol | spi  | х            | х              | х                | х            |                |                  | х            |                |                  |

|          | I2c  | х            | х              | х                | х            | х              | х                | х            | х              | х                |

|          | pwm  | х            | х              |                  | х            | х              |                  | х            |                |                  |

The location of the pins on the Pmod connectors is shown in Figure 19. Detailed pin descriptions depending on the pin multiplexer settings are provided in the subsequent sections.

Figure 19 Pinout Diagram of the Pmod\_A, Pmod\_B and Pmod\_C Connectors

### 3.16.1.1 Pmod\_A Connector

Table 11 lists the pin assignment of valid protocols that can be multiplexed on the Pmod\_A connector. The **GPIO** column is the default assignment after Reset.

Table 11 Pin Description of the Pmod\_A Connector

| Pin | GPIO     | UART      | SPI        | I2C      | PWM_1     | PWM_2     |

|-----|----------|-----------|------------|----------|-----------|-----------|

| A1  | gpio[8]  | uart2_cts | spi1_cs[1] | gpio[8]  | gpio[8]   | pwm_ch[2] |

| A2  | gpio[9]  | uart2_txd | spi1_mosi  | gpio[9]  | pwm_ch[4] | gpio[9]   |

| А3  | gpio[10] | uart2_rxd | spi1_miso  | i2c1_scl | gpio[10]  | gpio[10]  |

| A4  | gpio[11] | uart2_rts | spi1_clk   | i2c1_sda | gpio[11]  | gpio[11]  |

| A5  | GND      | GND       | GND        | GND      | GND       | GND       |

| A6  | 3V3      | 3V3       | 3V3        | 3V3      | 3V3       | 3V3       |

| A7  | gpio[20] | gpio[20]  | gpio[20]   | gpio[20] | gpio[20]  | gpio[20]  |

| A8  | gpio[21] | gpio[21]  | gpio[21]   | gpio[21] | gpio[21]  | gpio[21]  |

| A9  | n.c.     | n.c.      | n.c.       | n.c.     | n.c.      | n.c.      |

| A10 | n.c.     | n.c.      | n.c.       | n.c.     | n.c.      | n.c.      |

| A11 | GND      | GND       | GND        | GND      | GND       | GND       |

| A12 | 3V3      | 3V3       | 3V3        | 3V3      | 3V3       | 3V3       |

### 3.16.1.3 Pmod\_B Connector

Table 12 lists the pin assignment of valid protocols that can be multiplexed on the Pmod\_B connector. The **GPIO** column is the default assignment after Reset.

Table 12 Pin Description of the Pmod\_B Connector

| Pin | GPIO     | UART      | SPI        | I2C      | PWM_1     | PWM_2     |

|-----|----------|-----------|------------|----------|-----------|-----------|

| B1  | gpio[12] | uart0_cts | spi2_cs[1] | gpio[12] | gpio[12]  | pwm_ch[0] |

| B2  | gpio[13] | uart0_txd | spi2_mosi  | gpio[13] | pwm_ch[6] | gpio[13]  |

| В3  | gpio[14] | uart0_rxd | spi2_miso  | i2c2_scl | gpio[14]  | gpio[14]  |

| B4  | gpio[15] | uart0_rts | spi2_clk   | i2c2_sda | gpio[15]  | gpio[15]  |

| B5  | GND      | GND       | GND        | GND      | GND       | GND       |

| В6  | 3V3      | 3V3       | 3V3        | 3V3      | 3V3       | 3V3       |

| B7  | gpio[22] | gpio[22]  | gpio[22]   | gpio[22] | gpio[22]  | gpio[22]  |

| B8  | gpio[23] | gpio[23]  | gpio[23]   | gpio[23] | gpio[23]  | gpio[23]  |

| В9  | n.c.     | n.c.      | n.c.       | n.c.     | n.c.      | n.c.      |

| B10 | n.c.     | n.c.      | n.c.       | n.c.     | n.c.      | n.c.      |

| B11 | GND      | GND       | GND        | GND      | GND       | GND       |

| B12 | 3V3      | 3V3       | 3V3        | 3V3      | 3V3       | 3V3       |

#### 3.16.1.5 Pmod\_C Connector

Table 13 lists the pin assignment of valid protocols that can be multiplexed on the Pmod\_C connector. The **GPIO** column is the default assignment after Reset.

Table 13 Pin Description of the Pmod\_C Connector

| Pin | GPIO     | UART      | SPI        | I2C      | PWM       |

|-----|----------|-----------|------------|----------|-----------|

| C1  | gpio[16] | uart1_txd | spi1_cs[2] | i2c1_scl | gpio[16]  |

| C2  | gpio[17] | uart1_rxd | spi1_mosi  | i2c1_sda | pwm_ch[0] |

| СЗ  | gpio[18] | uart2_txd | spi1_miso  | i2c2_scl | gpio[18]  |

| C4  | gpio[19] | uart2_rxd | spi1_clk   | i2c2_sda | gpio[19]  |

| C5  | GND      | GND       | GND        | GND      | GND       |

| C6  | 3V3      | 3V3       | 3V3        | 3V3      | 3V3       |

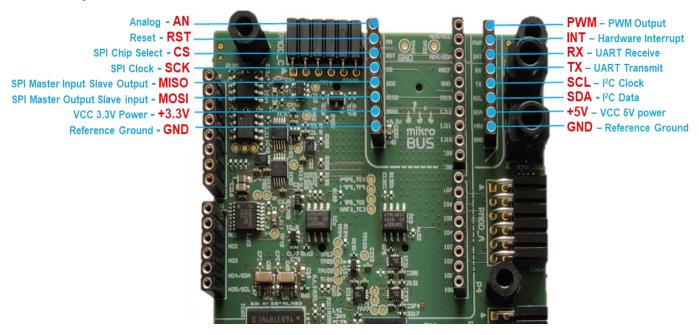

#### 3.16.2 **Mikrobus**

The ARC HSDK-4xD features a set of MikroBUS headers. Figure 20 shows the relevant function assignments, fully compatible with the MikroBUS standard [2]. The MikroBUS headers enable the addition of Click boards. Click boards are developed by the company MikroElektronica (www.mikroe.com) and are a range of hundreds of add on boards for interfacing with peripheral sensors and transceivers. Click boards include wireless and wired connectivity modules, sensor modules, display modules, interface modules, and miscellaneous modules and accessories, See www.mikroe.com/click for a full list. Multiplexing to get the right function assignment on the MikroBUS headers is controlled by software using the PMOD MUX CTRL register (see Mux Registers).

Figure 20 MikroBus Headers

Table 14 shows the pin assignment on the I/O Multiplexer.

Table 14 Pin Description of the MikroBUS Connectors

| Pin    | 1/0                               | Pin    | I/O                 |

|--------|-----------------------------------|--------|---------------------|

| AN     | ADC VIN6*                         | PWM    | pwm_ch[0]           |

| RST    | GPX_Port0_bit1                    | INT    | gpio[16]            |

| CS     | spi2_cs[1]                        | RX     | uart2_rxd           |

| SCK    | spi2_clk                          | TX     | uart2_txd           |

| MISO   | spi2_miso                         | SCL    | i2c2_scl            |

| MOSI   | spi2_mosi                         | SDA    | i2c2_sda            |

| ****** | O'r a allabla than ab tha an basa | 1450 1 | 1.4 1.0010 : 001.1: |

<sup>\*</sup>ADC VIN6 is available through the on-board ADC and is read though SPI0 using SPI chip select 1.

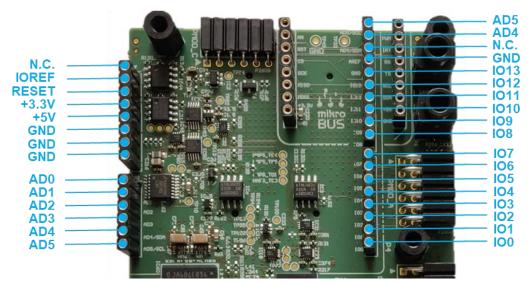

# 3.16.3 **Arduino**

The HSDK-4xD board provides an Arduino shield interface. Figure 21 shows the relevant function assignments. The Arduino shield interface is compatible with the Arduino UNO R3 with the following exceptions: 5 Volt shields are not supported, the IOREF voltage on the HSDK-4xD board is fixed to 3V3. Note that the ICSP header is also not available. Most

shields do not require this ICSP header as the SPI master interface on this ICSP header is also available on the IO10 to IO13 pins.

Figure 21 Arduino Shield Interface

Table 15 shows the pin assignment on the I/O Multiplexer. Multiplexing is controlled by software using the PMOD\_MUX\_CTRL register (see Mux Registers). After a reset, all ports are configured as GPIO inputs.

Table 15 Pin Description of the Arduino Shield Interface

| Pin  | I/O-1     | I/O-2              | I/O-3      |

|------|-----------|--------------------|------------|

| AD0  | ADC VINO* | GPX_port0_bi<br>t2 | -          |

| AD1  | ADC VIN1* | GPX_port0_bi<br>t3 | -          |

| AD2  | ADC VIN2* | GPX_port0_bi<br>t4 | _          |

| AD3  | ADC VIN3* | GPX_port0_bi<br>t5 | _          |

| AD4  | ADC VIN4* | gpio[18]           | i2c2_sda   |

| AD5  | ADC VIN5* | gpio[19]           | i2c2_scl   |

| 100  | gpio[23]  | uart2_rxd          | _          |

| 101  | gpio[22]  | uart2_txd          | _          |

| 102  | gpio[16]  | -                  | _          |

| 103  | gpio[17]  | pwm_ch[5]          | _          |

| 104  | gpio[11]  |                    | _          |

| 105  | gpio[9]   | pwm_ch[4]          | _          |

| 106  | gpio[21]  | pwm_ch[3]          | _          |

| 107  | gpio[20]  | _                  | _          |

| 108  | gpio[10]  | _                  | _          |

| 109  | gpio[8]   | pwm_ch[2]          | -          |

| 1010 | gpio[12]  | pwm_ch[0]          | spi2_cs[1] |

| 1011 | gpio[13]  | pwm_ch[6]          | spi2_mosi  |

| IO12 | gpio[14]  | _                  | spi2_miso  |

| 1013 | gpio[15]  | _                  | spi2_clk   |

<sup>\*</sup>ADC VIN0 – 6 are available through the on-board ADC and are read through SPI0 using SPI chip select 1.

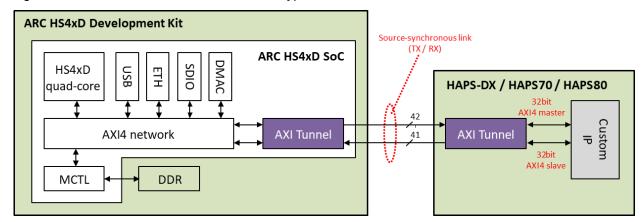

# 3.16.4 HapsTrak3 Extension

The DesignWare ARC HS4xD Development Kit includes two HapsTrak-3 [1] connectors to allow further extensions of the HSDK-4xD with additional FPGA resources using the

HAPS family of prototyping solutions. This interface allows adding system extensions at various levels of complexity. Main features of the extension connector are:

- · Carried signals:

- 82 AXI tunnel signals, carrying the AXI address and data

- Tunnel Reset, to reset the AXI Tunnel

- Tunnel BIST, connected to a LED

- o HAPS Resetn-Out

- Interrupt, connected to an HSDK-4xD GPIO input.

- Match trace length connections, as the AXI tunnel is source synchronous

- Voltage level swing (FPGA bank voltage) 1.8 Volt to support all HAPS systems

For more information on the HAPS extension interface signal mapping, see appendix A.1.

In Figure 22, a typical usage of the AXI tunnel to add custom IP into the HSDK-4xD context is depicted. Note that the AXI Tunnel provides a Bi-directional 32-bit AXI4 tunnel running at maximum 150 MHz, so total available bandwidth is 600 MB/s.

Figure 22 ARC HSDK-4xD HAPS Extension: Typical Use-case

Users that like to use other FPGA boards that feature an FMC connector can use an HapsTrak-3 to FMC adapter to connect the HSDK-4xD to a 3<sup>rd</sup> party FPGA featuring FMC extension headers.

# **Programmer's Reference**

# 4.1 Memory Map

Figure 23 shows the memory map overview depending on the ARC HSDK-4xD Core boot type.

Figure 23 ARC HSDK-4xD Memory Map (After U-Boot)

| 19470 20711 10 | TISDN-4XD MEI   | TOTY WAP (FIRE | 51 O B001)      | I              | 1               | I             |

|----------------|-----------------|----------------|-----------------|----------------|-----------------|---------------|

|                |                 |                |                 |                |                 |               |

|                |                 |                |                 | hs48           |                 |               |

|                |                 |                |                 | address offset | slave           |               |

|                |                 |                |                 | 0x1_F000_0000  | DDR [7]         |               |

|                |                 |                |                 | 0x1_E000_0000  | DDR [6]         |               |

|                |                 |                |                 | 0x1_D000_0000  | DDR [5]         |               |

|                |                 |                |                 | 0x1_C000_0000  | DDR [4]         |               |

|                |                 |                |                 | 0x1_B000_0000  | DDR [3]         |               |

|                |                 |                |                 | 0x1_A000_0000  | DDR [2]         |               |

|                |                 |                |                 | 0x1_9000_0000  | DDR [1]         |               |

|                |                 |                |                 | 0x1_8000_0000  | DDR [0]         | PAE region    |

|                |                 |                |                 | 0x1_7000_0000  | DDR [15]        |               |

|                |                 |                |                 | 0x1_6000_0000  | DDR [14]        |               |

|                |                 |                |                 | 0x1_5000_0000  | DDR [13]        |               |

|                |                 |                |                 | 0x1_4000_0000  | DDR [12]        |               |

|                |                 |                |                 | 0x1_3000_0000  | DDR [11]        |               |

|                |                 |                |                 | 0x1_2000_0000  | DDR [10]        |               |

| hs45D          |                 | hs47D          |                 | 0x1_1000_0000  | DDR [9]         |               |

| address offset | slave           | address offset | slave           | 0x1_0000_0000  | DDR [8]         |               |

| 0x0_F000_0000  | HSDK + HAPS APB | 0x0_F000_0000  | HSDK + HAPS APB | 0x0_F000_0000  | HSDK + HAPS APB |               |

| 0x0_E000_0000  | DDR[6]          | 0x0_E000_0000  | DDR[6]          | 0x0_E000_0000  | DDR[6]          |               |

| 0x0_D000_0000  | DDR [5]         | 0x0_D000_0000  | DDR [5]         | 0x0_D000_0000  | DDR [5]         |               |

| 0x0_C000_0000  | DDR [4]         | 0x0_C000_0000  | DDR [4]         | 0x0_C000_0000  | DDR [4]         |               |

| 0x0_B000_0000  | DDR [3]         | 0x0_B000_0000  | DDR [3]         | 0x0_B000_0000  | DDR [3]         | HW IOC region |

| 0x0_A000_0000  | DDR [2]         | 0x0_A000_0000  | DDR [2]         | 0x0_A000_0000  | DDR [2]         |               |

| 0x0_9000_0000  | DDR [1]         | 0x0_9000_0000  | DDR [1]         | 0x0_9000_0000  | DDR [1]         |               |

| 0x0_8000_0000  | DCCM            | 0x0_8000_0000  | DDR [0]         | 0x0_8000_0000  | DDR [0]         |               |

| 0x0_7000_0000  | ICCM            | 0x0_7000_0000  | DDR [15]        | 0x0_7000_0000  | DDR [15]        |               |

| 0x0_6000_0000  | DDR [14]        | 0x0_6000_0000  | DDR [14]        | 0x0_6000_0000  | DDR [14]        |               |

| 0x0_5000_0000  | DDR [13]        | 0x0_5000_0000  | DDR [13]        | 0x0_5000_0000  | DDR [13]        |               |

| 0x0_4000_0000  | DDR [12]        | 0x0_4000_0000  | DDR [12]        | 0x0_4000_0000  | DDR [12]        |               |

| 0x0_3000_0000  | DDR [11]        | 0x0_3000_0000  | DDR [11]        | 0x0_3000_0000  | DDR [11]        | _             |

| 0x0_2000_0000  | DDR [10]        | 0x0_2000_0000  | DDR [10]        | 0x0_2000_0000  | DDR [10]        |               |

| 0x0_1000_0000  | DDR [9]         | 0x0_1000_0000  | DDR [9]         | 0x0_1000_0000  | DDR [9]         |               |

| 0x0_0000_0000  | DDR [8]         | 0x0_0000_0000  | DDR [8]         | 0x0_0000_0000  | DDR [8]         |               |

# 4.1.1 APB Peripheral Address Map

Table 16 lists all the APB peripherals that are accessible through the AXI2APB bridge. The total reserved address space for the AXI2APB bridge is 256 MB. Accessing a non-existing APB peripheral results in an AXI error response.

Table 16 APB Peripheral Address Map

| Peripheral<br>Name | Base       | Size    | Description                                                                                           |

|--------------------|------------|---------|-------------------------------------------------------------------------------------------------------|

| CGU                | 0xF0000000 | 4 KB    | Clock Generation Unit                                                                                 |

| CREG               | 0xF0001000 | 4 KB    | Control registers                                                                                     |

| GPIO               | 0xF0003000 | 128Byte | General purpose I/O [6]                                                                               |

| MCTL               | 0xF0004000 | 2 KB    | DDR memory controller [9]                                                                             |

| PUB                | 0xF0004800 | 2 KB    | DDR PHY Utility Block                                                                                 |

| DEBUG-<br>UART     | 0xF0005000 | 256Byte | Debug UART [14]                                                                                       |

| WDT                | 0xF0006000 | 256Byte | Watchdog Timer [18]                                                                                   |

| ETH-GMAC           | 0xF0008000 | 8 KB    | Ethernet MA                                                                                           |

|                    |            |         | <ul> <li>0x00008000 =&gt; control/status registers</li> <li>0x00009000 =&gt; DMA registers</li> </ul> |

| SDIO0              | 0xF000A000 | 1 KB    | SDIO controller [13] ; used for SD card                                                               |

| SDIO1              | 0xF000A800 | 1 KB    | SDIO controller [13] ; used for Wifi/BT                                                               |

| PGU                | 0xF000B000 | 1 KB    | PGU controller                                                                                        |

| TIMERS             | 0xF000C000 | 256Byte | Timers                                                                                                |

| RTC                | 0xF000D000 | 64Byte  | Real Time Counter                                                                                     |

| HDMI               | 0xF0010000 | 32 KB   | HDMI-TX controller                                                                                    |

| SPI0               | 0xF0020000 | 256Byte | SPI                                                                                                   |

| SPI1               | 0xF0021000 | 256Byte | SPI                                                                                                   |

| SPI2               | 0xF0022000 | 256Byte | SPI                                                                                                   |

| I2C0               | 0xF0023000 | 256Byte | I2C                                                                                                   |

| I2C1               | 0xF0024000 | 256Byte | I2C                                                                                                   |

| I2C2     | 0xF0025000 | 256Byte  | 12C                                                                                                                        |

|----------|------------|----------|----------------------------------------------------------------------------------------------------------------------------|

| 1202     | 0X1 002000 | Zoobyto  | 120                                                                                                                        |

| UART0    | 0xF0026000 | 256Byte  | UART                                                                                                                       |

| UART1    | 0xF0027000 | 256Byte  | UART                                                                                                                       |

| UART2    | 0xF0028000 | 256 Byte | UART                                                                                                                       |