# DesignWare ARC SDP Mainboard User Guide

Version 6301-013 April 2017

### **Copyright Notice and Proprietary Information Notice**

© 2017 Synopsys, Inc. All rights reserved. This Synopsys software and all associated documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the terms and conditions of a written license agreement with Synopsys, Inc. All other use, reproduction, modification, or distribution of the Synopsys software or the associated documentation is strictly prohibited.

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### Trademarks

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at

http://www.synopsys.com/Company/Pages/Trademarks.aspx.

All other product or company names may be trademarks of their respective owners.

#### Third-Party Links

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

Synopsys, Inc. 690 E. Middlefield Road Mountain View, CA 94043 www.synopsys.com

## Contents

| 0         | ures                            |    |

|-----------|---------------------------------|----|

|           | oles                            |    |

| •         | Started                         |    |

| 2 Hardwar | e Functional Description        | 12 |

|           | Board Overview                  |    |

| 2.2 H     | lardware Interface Overview     |    |

| 2.2.1     | ARC CPU Card Interfaces         | 15 |

| 2.2.2     | Connectivity Interfaces         | 16 |

| 2.2.3     | Serial Interfaces               | 16 |

| 2.2.4     | Audio Interfaces                | 17 |

| 2.2.5     | HAPS Extension Interface        | 18 |

| 2.2.6     | Peripheral Extension Interfaces | 18 |

| 2.2.7     | Debug Interfaces                | 20 |

| 2.2.8     | SD-Card Slot                    |    |

| 2.2.9     | Miscellaneous Interfaces        |    |

| 2.3 C     | CPLD Board Supervisor           | 22 |

| 2.4 U     | JSB Dataport                    | 23 |

| 2.4.1     | JTAG Debug Channel              | 23 |

| 2.4.2     | Communication Channel           | 24 |

|           | TAG Programming Header          |    |

| 2.6 F     | PGA Temperature and Fan Control |    |

| 2.7 C     | Clock Generation                | 29 |

| 2.7.1     | FPGA Reference Clock            |    |

| 2.7.2     | AMBA Clocks                     |    |

| 2.7.3     | Tunnel Clocks                   |    |

| 2.7.4     | PGU Clock                       |    |

| 2.7.5     | Storage Clocks                  | 31 |

| 2.7.6     | Serial Connectivity Clocks      | 32 |

| 2.7.7     | Audio Reference Clock           |    |

| 2.7.8     | ARC CPU Card Clock              |    |

| 2.8 E     | ithernet                        |    |

| 2.9 U     | JSB                             | 34 |

| 2.10 H    | IDMI Output                     |    |

| 2.10.1    | 1 HDMI Audio Content            | 35 |

| 2.11 A    | udio Support                    |    |

| 2.11.1    | 1 Analog Stereo Inputs/Outputs  |    |

| 2.11.2    | 2 Analog 8-Channel Audio Output | 40 |

|           | 3 S/PDIF Inputs and Outputs     |    |

| 2.11.4    | 1 Audio PLL                     | 42 |

| 2.11.5    | 5 Advanced Audio Use Cases      | 43 |

| 2.12 S    | D-Card                          | 47 |

| 2.13 R    | Real Time Clock                 |    |

| 2.14 In   | nternal I <sup>2</sup> C Bus    | 49 |

| 2.15 l <sup>2</sup> C | CInterfaces                                              | 50 |

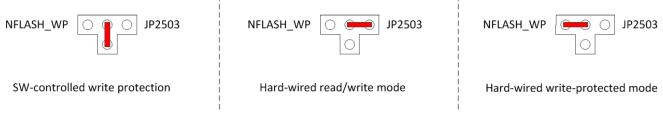

|-----------------------|----------------------------------------------------------|----|

| 2.15.1                | Routing Options for External I <sup>2</sup> C Interfaces | 50 |

| 2.15.2                | Using the Pmod4 Interface in I <sup>2</sup> C Mode       | 50 |

| 2.16 UA               | ART (RS232) Interfaces                                   | 52 |

| 2.16.1                | Routing Options for External UART Interfaces             | 53 |

| 2.16.2                | Default UART Interfaces                                  | 53 |

| 2.16.3                | Using Extension Interfaces in UART Mode                  | 57 |

|                       | PI Interfaces                                            |    |

| 2.17.1                | Routing Options for External SPI Interfaces              | 61 |

| 2.17.2                | Default SPI Connectors                                   | 61 |

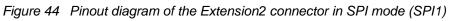

| 2.17.3                | Using Extension Interfaces in SPI Mode                   | 61 |

| 2.18 De               | bug                                                      | 65 |

| 2.18.1                | Using the USB Dataport for Debugging                     | 66 |

| 2.18.2                | Using an Ashling Opella XD Probe                         | 66 |

| 2.18.3                | Using Lauterbach Probes                                  | 68 |

| 2.18.4                | Using a Digilent Probe                                   | 69 |

| 2.19 Pu               | sh Buttons, Switches and LEDs                            | 70 |

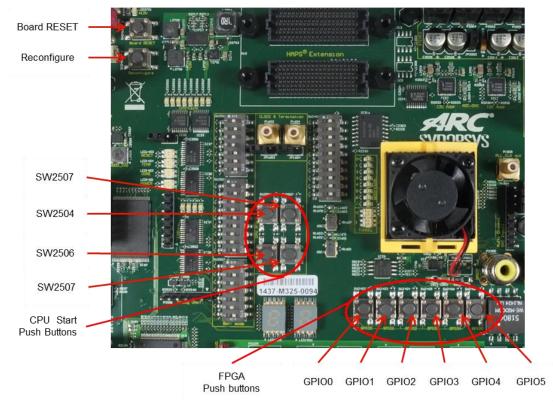

| 2.19.1                | Push Buttons                                             | 71 |

| 2.19.2                | Switches                                                 | 73 |

| 2.19.3                | LEDs                                                     | 74 |

| 2.20 Se               | even-Segment Display                                     | 79 |

| 2.21 Or               | n-Board Memories                                         | 80 |

| 2.21.1                | I <sup>2</sup> C EEPROM                                  | 80 |

| 2.21.2                | SPI Flash Application Memory                             | 80 |

| 2.21.3                | FPGA-Configuration FLASH                                 | 80 |

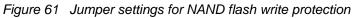

| 2.21.4                | NAND Flash                                               | 81 |

|                       | RAM                                                      |    |

| 2.22 Po               | wer Supply                                               | 81 |

| 2.23 Pe               | ripheral Subsystem FPGA Overview                         | 82 |

| 2.23.1                | AXI Tunnel                                               | 83 |

| 2.23.2                | Interrupt Controller (ICTL)                              | 83 |

|                       | Clock Generator Unit (CGU)                               |    |

|                       | DMA Controller (DMAC)                                    |    |

| 2.23.5                | SPI Controller for SPI Flash                             | 86 |

|                       | GPIO Modules                                             |    |

| 2.24 HA               | APS HapsTrak-3 Extension                                 | 87 |

|                       | nod Extension Options                                    |    |

|                       | Pmod0 Connector                                          |    |

|                       | Pmod1 Connector                                          |    |

|                       | Pmod2 Connector                                          |    |

|                       | Pmod3 Connector                                          |    |

|                       | Pmod4 Connector                                          |    |

|                       | Pmod Interface Type 1 (GPIO)                             |    |

| 2.25.7                | Pmod Interface Type 2 (SPI)                              | 94 |

|                       | Pmod Interface Type 2a (Expanded SPI)                    |    |

|                       | Pmod Interface Type 3 (UART)                             |    |

| 2.25.10 Pmod Interface Type 4 (UART)                 | 94  |

|------------------------------------------------------|-----|

| 2.25.11 Pmod Interface Type 4a (Expanded UART)       | 95  |

| 2.25.12 Pmod I <sup>2</sup> C Interface              | 95  |

| 2.26 Other Extension Options                         | 95  |

| 2.26.1 Extension0 Connector                          | 97  |

| 2.26.2 Extension1 Connector                          | 99  |

| 2.26.3 Extension2 Connector                          | 100 |

| 2.26.4 Extension3 Connector                          | 102 |

| 2.27 Power Supply for Extension Boards               | 104 |

| 2.28 Mounting an ARC CPU Card                        |     |

| 2.29 Backup Battery                                  | 105 |

| 3 System Memory Map                                  | 106 |

| 3.1 Controlling the Memory Map                       | 106 |

| 3.2 Memory Map After Reset                           | 109 |

| 3.3 Memory Map of Peripheral Subsystem               | 110 |

| 4 Software Interfaces                                |     |

| 4.1 Clock Generation Registers                       | 114 |

| 4.1.1 TUNNEL PLL                                     | 114 |

| 4.1.2 PGU PLL                                        | 119 |

| 4.1.3 Audio I2S Clock                                | 123 |

| 4.2 Control Registers                                | 125 |

| 4.2.1 AXI_m_SLV_SEL0 Register                        |     |

| 4.2.2 AXI_ <i>m</i> _SLV_SEL1 Register               | 126 |

| 4.2.3 AXI_m_SLV_OFFSET0 Register                     |     |

| 4.2.4 AXI_m_SLV_OFFSET1 Register                     | 128 |

| 4.2.5 AXI_UPDATE Register                            | 129 |

| 4.2.6 AXI_UPDATE_CLR Register                        | 129 |

| 4.2.7 AXI_UPDATE_STAT Register                       | 130 |

| 4.2.8 TUN_CTRL Register                              | 130 |

| 4.2.9 TUN_STAT Register                              | 131 |

| 4.2.10 PMOD_MUX_CTRL Register                        | 131 |

| 4.2.11 AUDIO_CLK_MUX_CTRL Register                   |     |

| 4.2.12 SPI_FLASH_MUX_CTRL Register                   | 133 |

| 4.2.13 SW_RESET Register                             | 133 |

| 4.3 ICTL Registers                                   |     |

| 4.3.1 ICTL_INT_STATUS: Interrupt Status Register     | 134 |

| 4.4 GPIO Registers                                   | 135 |

| 4.4.1 GPIO0 SWPORTA_DR: GPIO0 Port A Output Register | 135 |

| 4.4.2 GPIO0 SWPORTB_DR: GPIO0 Port B Output Register |     |

| 4.4.3 GPIO0 SWPORTC_DR: GPIO0 Port C Output Register | 137 |

| 4.4.4 GPIO0 EXT_PORTA: GPIO0 Port A Input Register   | 138 |

| 4.4.5 GPIO0 EXT_PORTB: GPIO0 Port B Input Register   |     |

| 4.4.6 GPIO0 EXT_PORTC: GPIO0 Port C Input Register   | 140 |

| 4.4.7 GPIO1 SWPORTC_DR: GPIO1 Port C Output Register |     |

| 4.4.8 GPIO1 EXT_PORTA: GPIO1 Port A Input Register   |     |

| 4.4.9 GPIO1 EXT_PORTB: GPIO1 Port B Input Register   | 143 |

|                                                      |     |

| 5 Software Installation                                   | 144   |

|-----------------------------------------------------------|-------|

| 5.1 USB-JTAG and USB-UART Driver Installation             | 144   |

| 5.2 AXS Communicator Tool – axs_comm                      | 144   |

| 5.2.1 Tool Overview and Installation Instructions         | 144   |

| 5.2.2 Usage                                               | 145   |

| Appendix A                                                | 146   |

| A.1 Jumper Overview                                       |       |

| Appendix B                                                | 154   |

| B.1 Programming the SPI Flash Memory                      | 154   |

| B.1.1 Using axs_comm for SPI FLASH programming            | 154   |

| Appendix C                                                | . 157 |

| C.1 Configuring the Real Time Clock                       | 157   |

| Appendix D                                                | 158   |

| D.1 HAPS Trak-3 Extension Connector Pins                  |       |

| Appendix E                                                |       |

| E.1 Using GPIO Pins at the ARC CPU Card Connectors        |       |

| E.2 ARC CPU Card Power Supply Connector                   | 161   |

| Appendix F                                                |       |

| F.1 Adding System Extensions via HAPS Extension Interface | 163   |

| Appendix G                                                | . 166 |

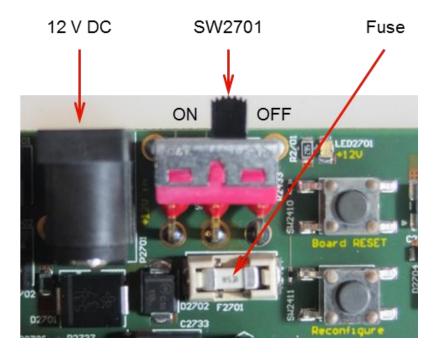

| G.1 Replacing the Fuse                                    | 166   |

| G.2 Backup Battery                                        | 167   |

| Glossary and References                                   | . 168 |

| Glossary                                                  | 168   |

| References                                                | 169   |

|                                                           |       |

# **List of Figures**

| Figure 1  | Principal block diagram                                                                    | 13 |

|-----------|--------------------------------------------------------------------------------------------|----|

| Figure 2  | ARC SDP Mainboard Hardware Interfaces                                                      | 14 |

| Figure 3  | Overview of peripheral extension interfaces                                                | 19 |

| Figure 4  | Location of the USB Dataport connector and the corresponding LEDs and jumpers              |    |

| Figure 5  | Jumper setting for connecting the debugger via the USB Dataport                            |    |

| Figure 6  | Jumper setting for connecting the debugger via debug cable connectors                      |    |

| Figure 7  | Location of the JTAG In and JTAG Out connectors and the corresponding jumpers              |    |

| Figure 8  | Pinout diagrams of the JTAG In and JTAG Out connectors                                     |    |

| Figure 9  | Location of the TEMP LED                                                                   |    |

| Figure 10 | Mainboard clock architecture                                                               |    |

| Figure 11 | Selecting SDIO card clock frequency via the SDIO controller                                | -  |

| Figure 12 | Location of Ethernet connector and Ethernet LEDs                                           |    |

| Figure 13 | Location of HDMI-related connectors and jumpers on the Mainboard                           |    |

| Figure 14 | Pinout diagram of the HDMI 8-Channel I2S Slave Input (JP2101)                              |    |

| Figure 15 | ARC SDP Mainboard audio interfaces                                                         |    |

| Figure 16 | Jumper settings for using the on-board stereo codecs (default)                             |    |

| Figure 17 | Location of the stereo inputs and outputs and of the corresponding jumpers                 |    |

|           | Location of the 8-Channel Output and the corresponding jumpers                             |    |

| Figure 19 | Location of the S/PDIF connectors                                                          |    |

| •         | Audio PLL jumper settings                                                                  |    |

| Figure 20 |                                                                                            |    |

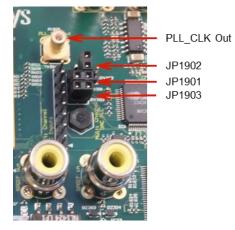

| Figure 21 | Location of the PLL_CLK Out connector and of the corresponding jumpers                     |    |

| Figure 22 | Jumper settings for using an external custom stereo codec                                  |    |

| Figure 23 | Location of the External Stereo Codec I2S In / Out connector and the corresponding jumpers |    |

| Figure 24 | Pinout diagram of the external stereo codec I <sup>2</sup> S master input / output         |    |

| Figure 25 | Location of the External 8-Channel Codec I2S Out connector                                 |    |

| Figure 26 | Pinout diagram of the External 8-Channel Codec I2S Out connector                           |    |

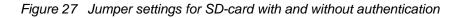

| Figure 27 | Jumper settings for SD-card with and without authentication                                |    |

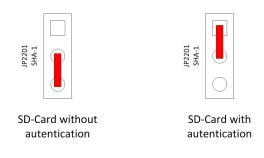

| Figure 28 | Location of SD-card slot and corresponding jumper                                          |    |

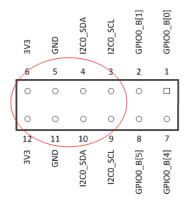

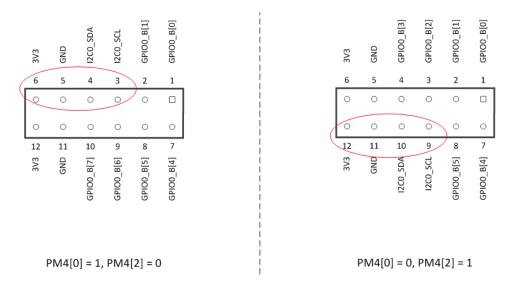

| Figure 29 | Location of the Pmod4 Connector Supporting I <sup>2</sup> C Mode                           |    |

| Figure 30 | Pinout diagram of the Pmod4 connector (standard 8-pin interface)                           |    |

| Figure 31 | Pinout diagram of the Pmod4 connector (4-pin subsets)                                      |    |

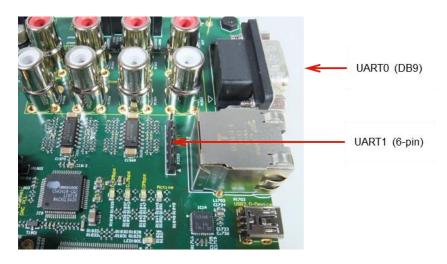

| Figure 32 | Location of the UART0 and UART1 connectors                                                 |    |

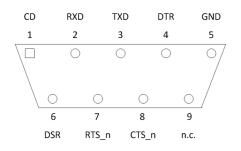

| Figure 33 | Pinout diagram of the UART0 DB9 connector                                                  |    |

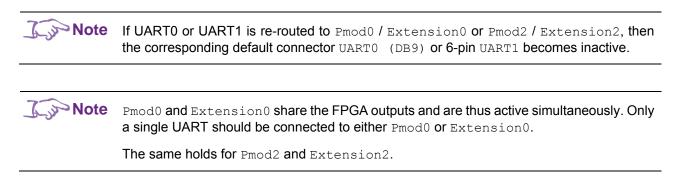

| Figure 34 | Pinout diagram of the UART1 connector                                                      |    |

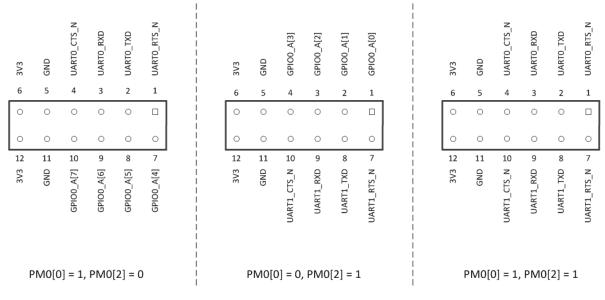

|           | Location of Pmod and Extension connectors supporting UART mode                             |    |

|           | Pinout diagrams of the Pmod0 connector in UART mode (UART0 / UART1)                        |    |

| Figure 37 | Pinout diagrams of the Extension0 connector in UART mode (IART0 / UART1)                   | 58 |

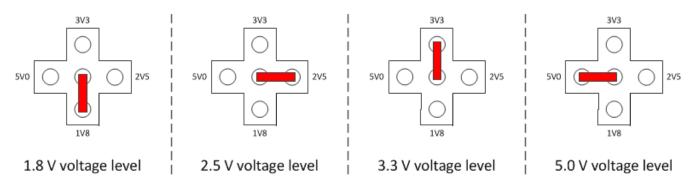

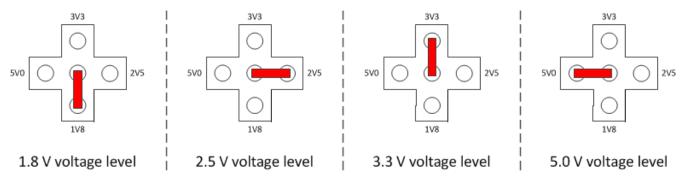

| Figure 38 | Voltage level selection for the Extension0 connector                                       |    |

| Figure 39 | Pinout diagram of the Pmod2 connector in UART mode (UART0)                                 | 59 |

| Figure 40 | Pinout diagram of the Extension2 connector in UART mode (UART0)                            | 60 |

| Figure 41 | Voltage level selection for the Extension2 connector                                       | 60 |

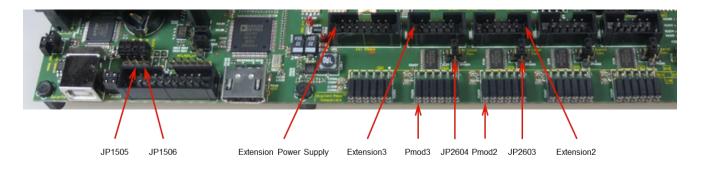

| Figure 42 | Location of Pmod and Extension connectors supporting SPI mode                              | 62 |

| Figure 43 | Pinout diagram of the Pmod2 connector in SPI mode (SPI1)                                   | 62 |

| Figure 44 | Pinout diagram of the Extension2 connector in SPI mode (SPI1)                              | 63 |

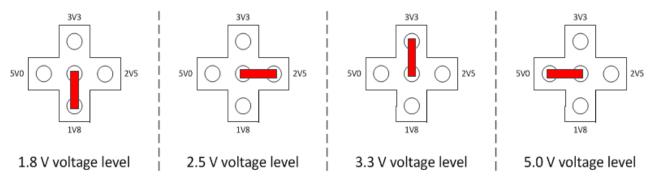

| Figure 45 | Voltage level selection for the Extension2 connector                                       |    |

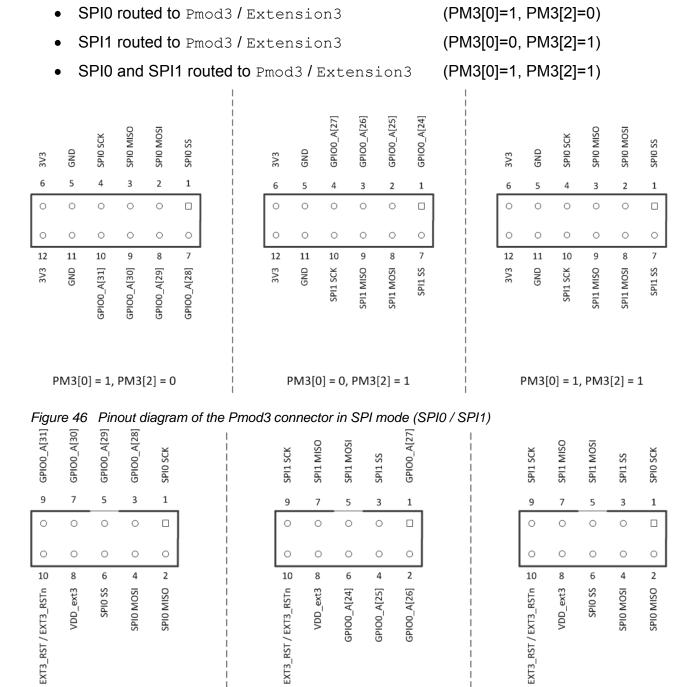

| Figure 46 | Pinout diagram of the Pmod3 connector in SPI mode (SPI0 / SPI1)                            |    |

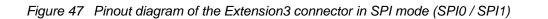

| Figure 47 | Pinout diagram of the Extension3 connector in SPI mode (SPI0 / SPI1)                       |    |

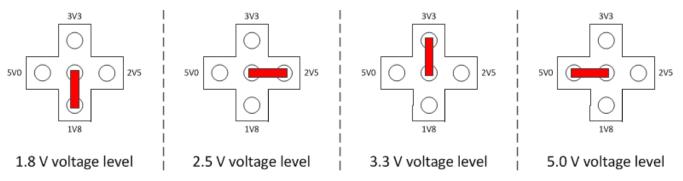

| Figure 48 | Voltage level selection for the Extension3 connector                                       |    |

| <b>.</b>  |                                                                                            |    |

| Location of the debug interfaces and the corresponding jumpers                     | 66                                                             |

|------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Jumper setting for connecting the debugger via the USB Dataport                    | 66                                                             |

| Pinout diagram and jumper settings for connecting an Ashling probe                 | 68                                                             |

| Pinout diagram and jumper settings for connecting a Lauterbach probe               | 69                                                             |

| Pinout diagram and jumper settings for connecting a Digilent probe                 | 70                                                             |

|                                                                                    |                                                                |

| Location of the push buttons                                                       | 71                                                             |

|                                                                                    |                                                                |

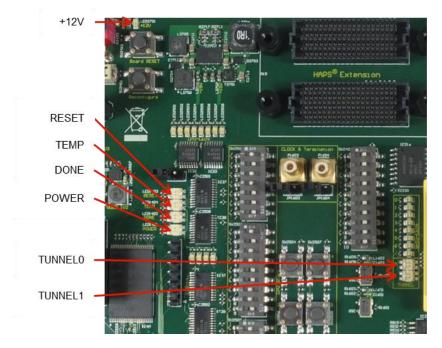

| Location of the Board Status LEDs                                                  | 76                                                             |

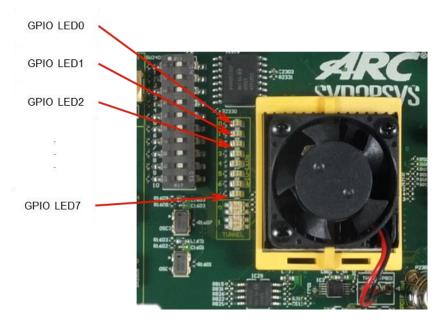

| Location of the GPIO LEDs                                                          | 77                                                             |

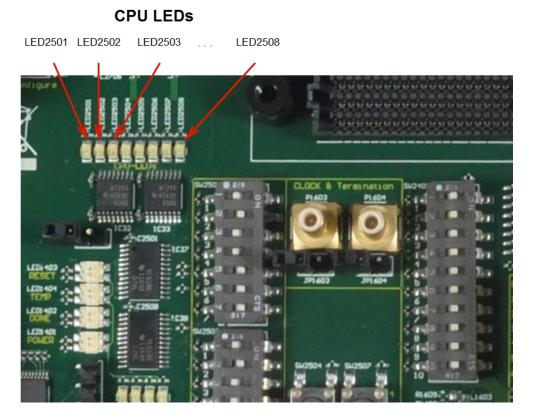

| Location of the CPU LEDs                                                           | 78                                                             |

| Location of the USB Dataport Mode LEDs                                             | 79                                                             |

|                                                                                    |                                                                |

|                                                                                    |                                                                |

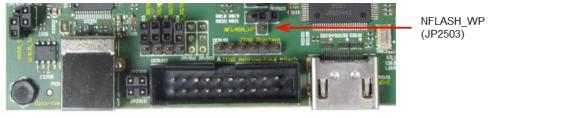

| Location of power inlet, power switch and power status LEDs                        | 82                                                             |

| Principle block diagram of the peripheral subsystem                                | 83                                                             |

| P Devices on GPIO0                                                                 | 88                                                             |

|                                                                                    |                                                                |

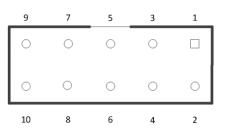

| Pinout diagram of the Extension0, Extension1, Extension2 and Extension3 connectors | 97                                                             |

|                                                                                    |                                                                |

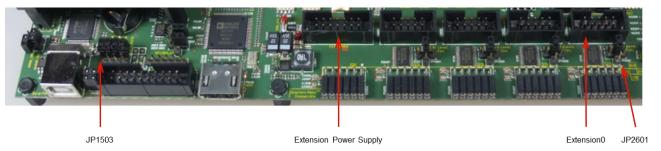

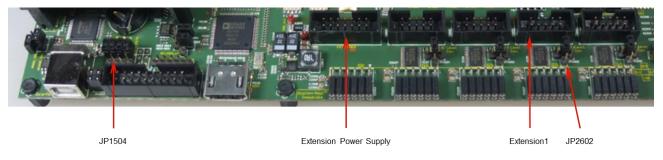

| Location of the Extension0 connector and its associated jumpers                    | 98                                                             |

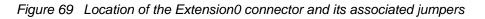

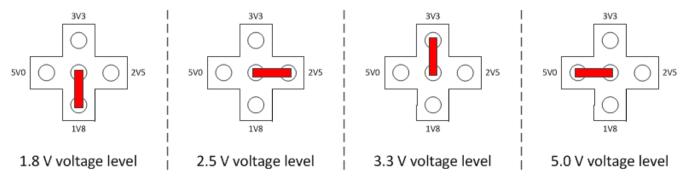

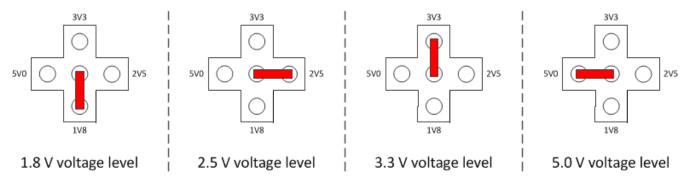

| Voltage level selection for the Extension0 connector                               | 99                                                             |

|                                                                                    |                                                                |

| Voltage level selection for the Extension1 connector                               | 100                                                            |

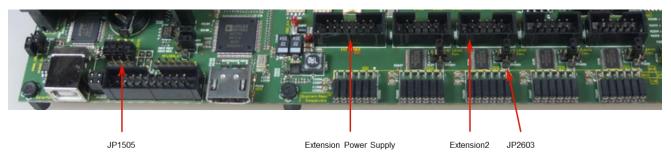

| Location of the Extension2 connector and its associated jumpers                    | 101                                                            |

| Voltage level selection for the Extension2 connector                               | 102                                                            |

| Location of the Extension3 connector and its associated jumpers                    | 102                                                            |

| Voltage level selection for the Extension3 connector                               | 103                                                            |

| Pinout diagram of the Extension Power Supply connector                             | 104                                                            |

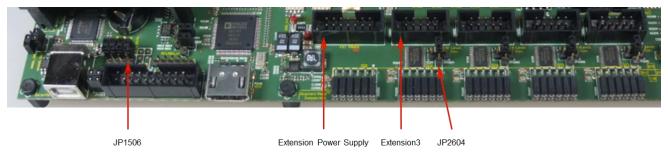

| Jumper location overview                                                           | 146                                                            |

| Power supply of the ARC CPU Card                                                   | 162                                                            |

| Location of the fuse                                                               |                                                                |

|                                                                                    | Location of the debug interfaces and the corresponding jumpers |

# List of Tables

| Table 1  | ARC CPU Card interfaces                                                             |    |

|----------|-------------------------------------------------------------------------------------|----|

| Table 2  | Connectivity Interfaces                                                             |    |

| Table 3  | Serial interfaces                                                                   |    |

| Table 4  | Peripheral extension interfaces                                                     |    |

| Table 5  | Debug interfaces                                                                    |    |

| Table 6  | Miscellaneous interfaces                                                            |    |

| Table 7  | Pin description of the JTAG In connector                                            |    |

| Table 8  | Pin description of the JTAG Out connector                                           |    |

| Table 9  | AMBA clocks                                                                         |    |

| Table 10 | AXI tunnel clocks (after reset)                                                     |    |

| Table 11 | AXI tunnel clocks (after pre-boot)                                                  |    |

| Table 12 | PGU reference clock                                                                 |    |

| Table 13 | Storage reference clocks                                                            |    |

| Table 14 | Serial Connectivity reference clocks                                                |    |

| Table 15 | Audio Reference Clocks                                                              |    |

| Table 16 | Ethernet LEDs                                                                       |    |

| Table 17 | Pin Description of the HDMI 8-Channel I <sup>2</sup> S Slave Input                  |    |

| Table 18 | Audio interfaces on the Mainboard                                                   |    |

| Table 19 | Pin description of the external stereo codec I <sup>2</sup> S master input / output |    |

| Table 20 | Pin description of the External 8-Channel Codec I2S Out connector                   |    |

| Table 21 | Internal I <sup>2</sup> C bus slave addresses                                       |    |

| Table 22 | I <sup>2</sup> C Interface selection                                                |    |

| Table 23 | UART Interface selection                                                            |    |

| Table 24 | Pin description of the UART0 (DB9) connector                                        |    |

| Table 25 | Pin description of the 6-pin UART1 connector                                        |    |

| Table 26 | SPI Interface selection                                                             |    |

| Table 27 | Pin description of the CPU Debug Ashling/Lauterbach connector in Ashling mode       | 66 |

| Table 28 | Pin description of the CPU Debug Ashling/Lauterbach connector in Lauterbach mode    |    |

| Table 29 | Pin description of the CPU Debug Digilent connector                                 | 70 |

| Table 30 | List of push buttons                                                                |    |

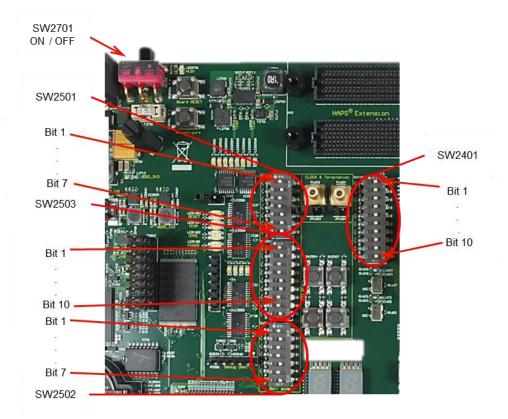

| Table 31 | List of switches                                                                    |    |

| Table 32 | Board status LEDs                                                                   | -  |

| Table 33 | GPIO LEDs (controlled by Mainboard GPIO1 module)                                    |    |

| Table 34 | USB Dataport LEDs                                                                   |    |

| Table 35 | ICTL Interrupt mapping                                                              |    |

| Table 36 | DMAC flow control interface mapping                                                 |    |

| Table 37 | GPIO1 I/O register function                                                         |    |

| Table 38 | Pmod pin multiplexing overview                                                      |    |

| Table 39 | UART signal description                                                             |    |

| Table 40 | SPI Signal Description                                                              | 90 |

| Table 41 | I <sup>2</sup> C Signal Description                                                 |    |

| Table 42 | Pin description of the Pmod0 connector                                              |    |

| Table 43 | Pin description of the Pmod1 connector                                              |    |

| Table 44 | Pin description of the Pmod2 connector                                              |    |

| Table 45 | Pin description of the Pmod3 connector                                              |    |

| Table 46 | Pin description of the Pmod4 connector                                              | 93 |

| Table 47 | Extension connector pin multiplexing overview                     |  |

|----------|-------------------------------------------------------------------|--|

| Table 48 | UART signal description                                           |  |

| Table 49 | SPI Signal Description                                            |  |

| Table 50 | Pin description of the Extension0 connector                       |  |

| Table 51 | Pin description of the Extension1 connector                       |  |

| Table 52 | Pin description of the Extension2 connector                       |  |

| Table 53 | Pin description of the Extension3 connector                       |  |

| Table 54 | Pin description of the extension power supply connector           |  |

| Table 55 | AXI Masters                                                       |  |

| Table 56 | Target slaves                                                     |  |

| Table 57 | Slave Select and Address Offset Registers                         |  |

| Table 58 | Address Offset Settings for Example 3                             |  |

| Table 59 | Memory map after reset                                            |  |

| Table 60 | Peripheral memory map                                             |  |

| Table 61 | Peripheral registers overview                                     |  |

| Table 62 | I2S sclk Divider Settings                                         |  |

| Table 63 | Jumper functional overview and default settings                   |  |

| Table 64 | Pin description of the HAPS Trak-3 extension connectors J3 and J4 |  |

| Table 65 | GPIO field of ARC CPU Card Interface                              |  |

| Table 66 | Pin description of the ARC CPU Card power supply connector        |  |

# **1** Getting Started

The getting started procedure depends on the type of ARC CPU Card used. Refer to the documentation of a corresponding ARC CPU Card for more information.

This chapter provides information about the hardware of the ARC SDP Mainboard.

## 2.1 Board Overview

The ARC SDP Mainboard is the foundation of the ARC Software Development Platform. It provides connectors and power supply for the ARC CPU Card and provides the main infrastructure and connectivity.

The ARC Software Development Platform is a powerful, high-speed development platform, enabling real-time software development and validation, code porting, software debugging, and system analysis. Readily available DesignWare IP has been used to build the ARC Software Development Platform, which is thus well-suited for SoC prototyping including ARC CPUs.

The ARC CPU Card is connected to the ARC SDP Mainboard through a 18-pin header for power supply and two HapsTrak-3 connectors for a fast AXI tunnel operating at up to 150 MHz and supplying additional clocks, data and control signals. The AXI tunnel is the backbone of the ARC Software Development Platform. It connects the CPUs on the ARC CPU Card with a peripheral subsystem that is implemented on an FPGA on the ARC SDP Mainboard. The mainboard FPGA is located in the center of the mainboard, under the fan.

A rich set of interfaces is available including audio, USB 2.0 host, HDMI, Ethernet, and several serial protocols.

The ARC SDP Mainboard features an SD-card reader and includes multiple memories for storing boot code, application code, operating system, and data.

Two HapsTrak-3 connectors allows connecting a HAPS system to the ARC SDP Mainboard also using a fast AXI tunnel. Custom hardware extensions such as additional application specific peripherals can use this AXI tunnel for communicating seamlessly with the cores, memories, and peripherals available on the ARC SDP Mainboard and ARC CPU Card. Custom hardware extensions can thus be integrated conveniently and operated at high speed.

Multiple other extension interfaces such as five Digilent Pmod<sup>™</sup> compatible connectors and four extension headers with selectable voltage levels are available as well. These extension interfaces support GPIO, SPI, I<sup>2</sup>C, and UARTs.

The board operates on a single 12V DC power supply. An AC power adapter is included. All required voltage levels and clocks are generated on the board, so that no lab equipment is required to get started with development.

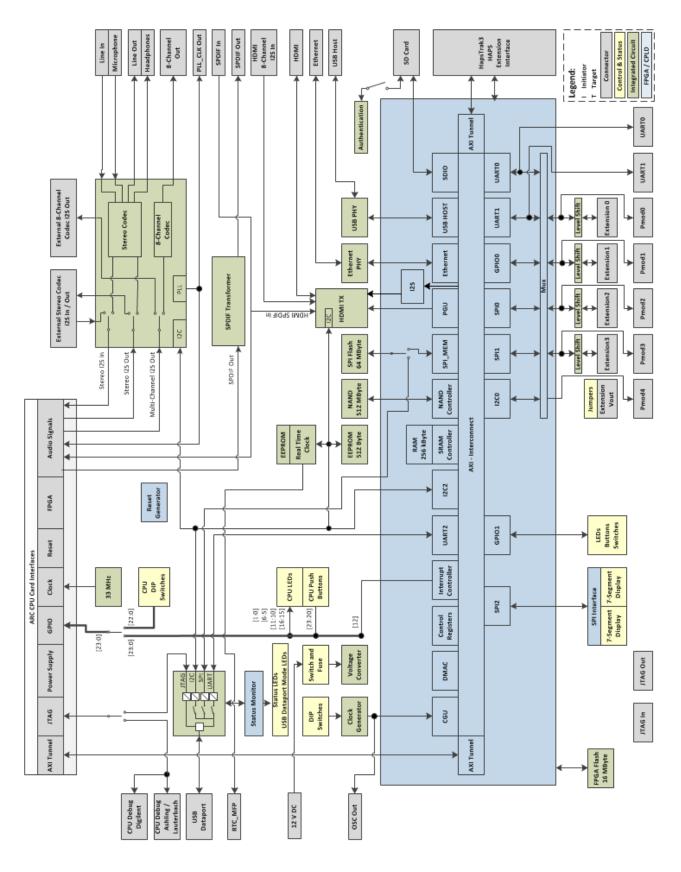

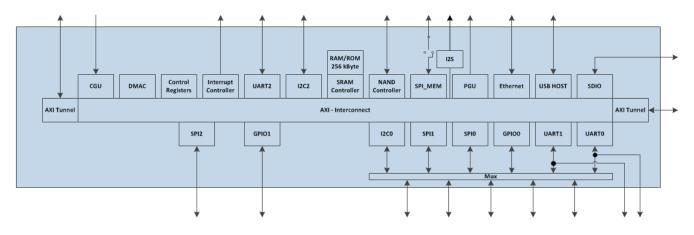

Figure 1 shows the principal block diagram of the ARC SDP Mainboard.

Figure 1 Principal block diagram

### 2.2 Hardware Interface Overview

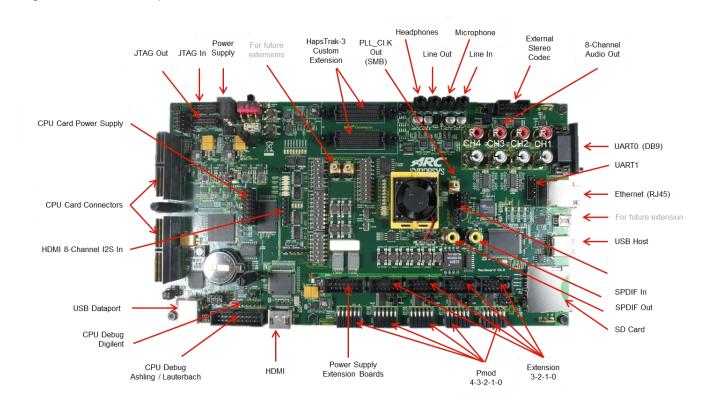

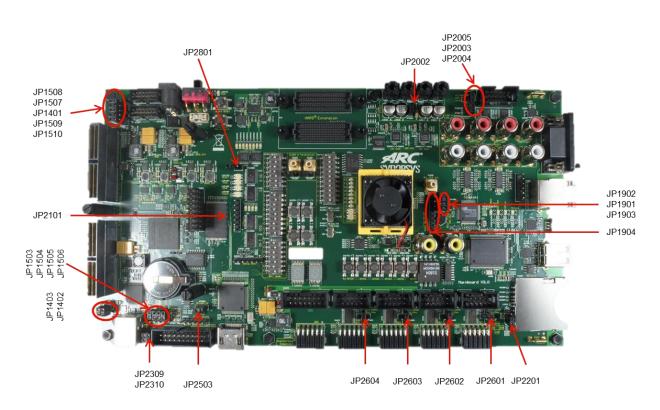

Figure 2 shows the position of the hardware interfaces on the ARC SDP Mainboard.

Figure 2 ARC SDP Mainboard Hardware Interfaces

The ARC SDP Mainboard features many hardware interfaces, which can be grouped in the following categories:

- ARC CPU Card interfaces

- Connectivity interfaces

- Serial interfaces

- Audio interfaces

- Extension interfaces

- Debug interfaces

- SD-card slot

- Miscellaneous interfaces

### 2.2.1 ARC CPU Card Interfaces

The ARC SDP Mainboard communicates with the ARC CPU Card using two HapsTrak-3 connectors, which carry signal groups such as

- AXI tunnel

- GPIO

- Clock

- Reset

- Audio signals

- Stereo I<sup>2</sup>S slave input

- Stereo I<sup>2</sup>S slave input

- 8-channel I<sup>2</sup>S slave output

- SPDIF input

- SPDIF output

Additionally, the Mainboard provides power to the CPU Card via a separate connector.

Table 1 below provides a brief overview of the ARC CPU Card interfaces.

| Table 1 | ARC CPU Card interfaces |

|---------|-------------------------|

|         |                         |

| Name                  | Description                    | Voltage Level                   |

|-----------------------|--------------------------------|---------------------------------|

| CPU Card Connectors   | Two HapsTrak-3 connectors      |                                 |

| CPU Card Power Supply | 18-pin header for power supply | 12V<br>3V3<br>2V5<br>1V8<br>1V1 |

### 2.2.2 Connectivity Interfaces

The ARC SDP Mainboard supports the following communication protocols:

- Ethernet 10/100 Mb/s

- HDMI TX

- USB 2.0 Host

Table 2 provides an overview of the connectivity interfaces. Additional serial protocols such as SPI, I<sup>2</sup>C, and UART are supported as well.

See "Serial Interfaces" and "Peripheral Extension Interfaces" sections for an overview about the serial interfaces of the Mainboard.

Table 2 Connectivity Interfaces

| Name     | Description                              | Voltage Level |

|----------|------------------------------------------|---------------|

| Ethernet | RJ45 Ethernet jack                       |               |

| HDMI     | HDMI type A female connector for HDMI TX |               |

| USB Host | USB 2.0 host interface (type A)          |               |

### 2.2.3 Serial Interfaces

Table 3 provides an overview of the dedicated serial interfaces on the ARC SDP Mainboard.

Additional I<sup>2</sup>C, SPI, and UART ports are available at the multi-purpose extension interfaces Pmod0 to Pmod4 and Extension0 to Extension3. See the "Peripheral Extension Interfaces" section for an overview.

| Name  | Description                                                                           | Voltage Level |

|-------|---------------------------------------------------------------------------------------|---------------|

| UART0 | DB9 connector for UART0                                                               | 3V3           |

| UART1 | 6-pin header for UART1<br>Pinout compatible with FTDI USB to TTL Serial Cable<br>[6]. | 3V3           |

Table 3Serial interfaces

### 2.2.4 Audio Interfaces

The ARC SDP Mainboard has the following external audio interfaces:

- Stereo line out

- Stereo headphones out

- Stereo line in

- Stereo microphone in

- 8-channel out

- SPDIF input

- SPDIF output

The digital sources for these audio outputs and the sinks for the inputs are located on the ARC CPU Card. The following interfaces exist in the ARC CPU Card header:

- Stereo I<sup>2</sup>S slave input

- Stereo I<sup>2</sup>S slave output

- 8-channel I2S slave input

- SPDIF input

- SPDIF output

For advanced use cases, external custom codecs can be used instead of the on-board audio codecs. The ARC SDP Mainboard features a stereo I<sup>2</sup>S master input, a stereo I<sup>2</sup>S master output, and an eight-channel I<sup>2</sup>S master output to connect your custom codecs.

In addition, the output of the on-board audio PLL is accessible at an SMB connector.

See the "Audio Support" section for details.

The audio output of the on-board HDMI connector can be provided by the SPDIF-IN RCA signal, or by the eight-channel I<sup>2</sup>S slave in the FPGA. See the "HDMI Audio Content" section for details.

#### 2.2.5 HAPS Extension Interface

The ARC SDP Mainboard includes two HapsTrak-3 connectors for connecting prototyping systems from the HAPS product family. These FPGA-based prototyping systems allow further system extensions (for example, CPUs, memories, peripherals).

The connector provides a high-speed AXI tunnel and a few control signals. The voltage level swing is 1.8 Volts, supporting all HAPS systems.

The HAPS Extension Interface should not be used to connect a HAPS daughter board.

### 2.2.6 Peripheral Extension Interfaces

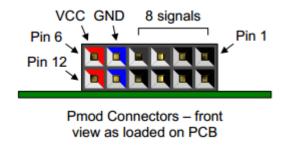

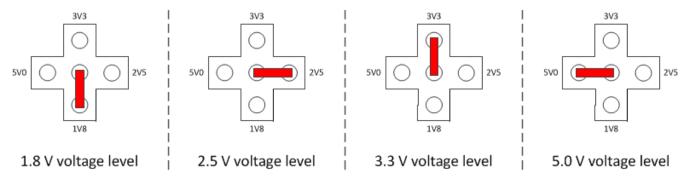

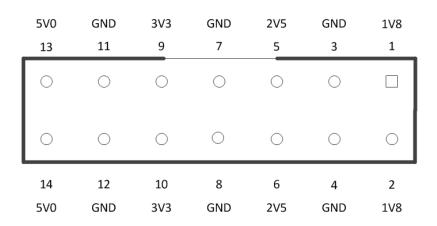

The ARC SDP Mainboard features five 12-pin Pmod connectors plus four 10-pin extension headers, which can be used to Pmod or other extension modules with additional peripherals to the system. Table 4 provides an overview of the available peripheral extension interfaces.

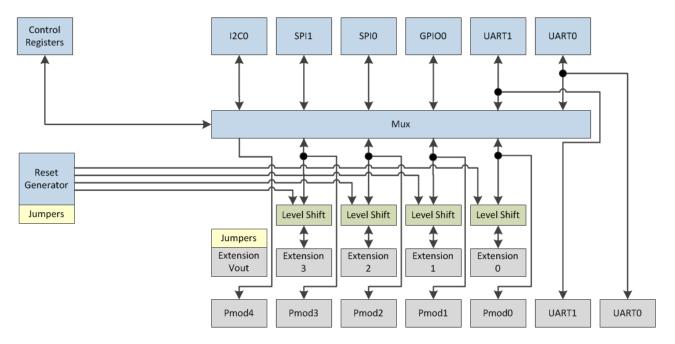

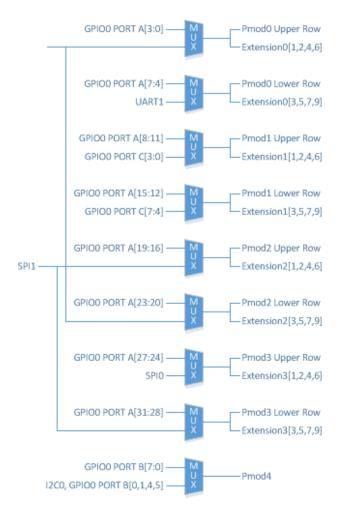

A total of 40 I/O pins of the peripheral subsystem are routed to these connectors, where pinsharing is done between the Pmod connectors and the Extension connectors as shown in Figure 3.

| Name             | Description                             | I/O Voltage Level       |

|------------------|-----------------------------------------|-------------------------|

| Pmod 0           | Five Pmod connectors 2x6                | 3V3                     |

| Pmod 1           |                                         |                         |

| Pmod 2           |                                         |                         |

| Pmod 3           |                                         |                         |

| Pmod 4           |                                         |                         |

| Extension 0      | Four 2x5 headers for hardware extension | Selectable with jumper: |

| Extension 1      | boards                                  | 5V0                     |

| Extension 2      |                                         | 3V3                     |

| Extension 3      |                                         | 2V5                     |

|                  |                                         | 1V8                     |

| Power Supply     | 14-pin header with power supply for     | 5V0                     |

| Extension Boards | extension boards                        | 3V3                     |

|                  | Two output pins per voltage. Six ground | 2V5                     |

|                  | pins.                                   | 1V8                     |

|                  |                                         |                         |

Table 4 Peripheral extension interfaces

Figure 3 Overview of peripheral extension interfaces

### 2.2.6.1 Pmod Connectors

The Pmod interfaces natively support the following Pmod interface types:

- Pmod Interface Type 1 (GPIO)

- Pmod Interface Type 2 (SPI)

- Pmod Interface Type 2A (expanded SPI)

- Pmod Interface Type 4 (UART)

- Pmod Interface Type 4A (expanded UART)

- I<sup>2</sup>C

Modules featuring the deprecated Pmod Interface 3 (UART) can be connected to the ARC SDP Mainboard using a crossover cable (available from Digilent Inc.) or flying lead cables (see [3]).

For more information on the on-board Pmod interfaces, refer to the following sections:

- "Pmod Extension Options" for the Pmod interfaces in general

- "

- UART (RS232) Interfaces" for using Pmod interfaces in UART mode

- "SPI Interfaces" for using Pmod interfaces in SPI mode

- "I2C Interfaces" for using Pmod interfaces in I<sup>2</sup>C mode

### 2.2.6.2 Extension Connectors

The headers Extension0, Extension1, Extension2, and Extension3 have jumperselectable voltage levels and support the following interface types:

- GPIO

- SPI

- UART

These extension connectors provide the same logical signals as the corresponding Pmod connectors Pmod0, Pmod1, Pmod2, and Pmod3. In addition to the Pmod connectors the Extension connectors provide a reset output and have selectable voltage levels.

For more information on the Extension connectors, refer to the "Other Extension Options" section.

A separate header for the power supply of the extension boards is available.

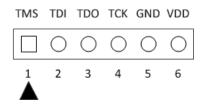

### 2.2.7 Debug Interfaces

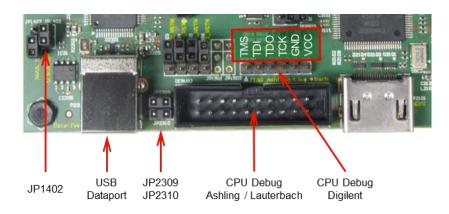

Multiple interfaces are available for software debugging. The ARC SDP Mainboard features a USB Dataport and a USB converter chip providing a JTAG debug channel and a UART console through a single USB cable. Alternatively, debug probes by Digilent, Ashling or Lauterbach can be connected to one of the two CPU debug connectors.

Table 5Debug interfaces

| Name                            | Description                                                 | Voltage Level |

|---------------------------------|-------------------------------------------------------------|---------------|

| USB Dataport                    | USB 2.0 dataport (type B)                                   |               |

| CPU Debug<br>Ashling/Lauterbach | 20-pin connector for debug probes by Ashling and Lauterbach | 1V8           |

| CPU Debug Digilent              | 6-pin connector for Digilent debug probe                    | 1V8           |

See the "Debug" section for detailed information on connecting the debugger.

### 2.2.8 SD-Card Slot

The ARC SDP Mainboard includes a slot for standard SD-cards. A jumper allows to enable / disable authentication support. See the "SD-Card" section for detailed information.

### 2.2.9 Miscellaneous Interfaces

| Name         | Description                                            | Voltage Level |

|--------------|--------------------------------------------------------|---------------|

| Power Supply | DC input                                               | 12 V          |

|              | See the "Power Supply" section for details.            |               |

| OSC Out      | SMB jack for FPGA main clock                           | 3V3           |

|              | Frequency selected by DIP switches.                    |               |

|              | See the "                                              |               |

|              | FPGA Reference Clock" section for details.             |               |

| JTAG In      | JTAG chain input and output                            | 3V3           |

| JTAG Out     | See the "JTAG Programming Header" section for details. |               |

## 2.3 CPLD Board Supervisor

The ARC SDP Mainboard includes a CPLD (Coolrunner-II) that is used to implement the following main functions:

- Reset controller Controls the reset sequencing of the FPGA, ARC CPU Card, on-board integrated circuits, and hardware extensions connected to the extension interfaces

- Status monitor Monitors power supply, reset, FPGA temperature, and FPGA configuration status and indicates the status using LEDs (power, reset, FPGA done, and temperature alert)

- JTAG multiplexer Selects between JTAG sources (JTAG In / Out, USB-to-JTAG converter) and between JTAG targets (such as CPU debugging or FPGA programming)

- SPI interface for seven-segment displays Provides an SPI interface for the two on-board seven-segment displays

- Control for SPI Flash programming

The CPLD is located at the top left of the board, near the jumpers.

## 2.4 USB Dataport

The USB Dataport has a USB-B connector and can be connected to your PC using the USB cable included in the product package. A USB converter by FTDI (FT2232HL) converts one USB channel to a serial communication protocol (UART, I<sup>2</sup>C or SPI). The other channel is converted to JTAG.

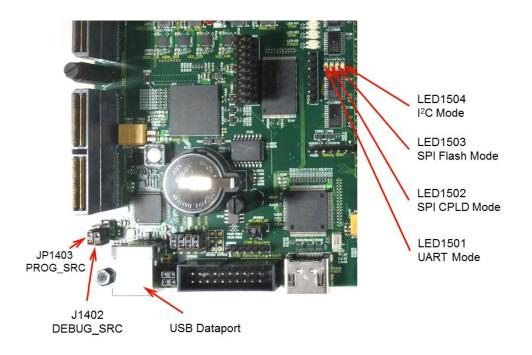

The location of the USB Dataport connector on the ARC SDP Mainboard is shown in Figure 4. The location of the LEDs and jumpers that are related to the USB Dataport are shown as well.

Figure 4 Location of the USB Dataport connector and the corresponding LEDs and jumpers

### 2.4.1 JTAG Debug Channel

For software debugging, the debugger tool can be connected to the ARC cores on the ARC CPU Card via the JTAG debug channel of the USB Dataport or via one of the debug cable connectors (CPU Debug Ashling / Lauterbach and CPU Debug Digilent). The jumpers JP1403/JP1402 select between these two modes. The jumper setting for connecting the debugger via the USB Dataport is shown in Figure 5 below.

Figure 5 Jumper setting for connecting the debugger via the USB Dataport

Figure 6 Jumper setting for connecting the debugger via debug cable connectors

### 2.4.2 Communication Channel

The communication channel is used by the axs\_comm tool (see "AXS Communicator Tool – axs\_comm") to access multiple on-board resources. It operates in four modes as described below:

UART Mode

In UART mode the user can invoke a standard hyperterminal on the PC, which can be used as a console for software debugging. This is the default mode after a reset. LED1501 shines green when the USB Dataport is in UART mode.

I<sup>2</sup>C Mode

The I<sup>2</sup>C mode is used to control and program the on-board real time clock, HDMI transmitter, and the EEPROM. LED1504 shines green when the <code>USB Dataport</code> is in I<sup>2</sup>C mode.

• SPI Flash Mode

The SPI Flash mode is used to initialize or read back the SPI flash application memory using the USB interface. LED1503 shines green when the USB Dataport is in SPI Flash mode.

• SPI CPLD Mode

The SPI CPLD mode is used to access registers in the CPLD device. LED1502 shines green when the  $\tt USB \ Dataport$  is in SPI CPLD mode.

Switching between these four modes is automatically performed by the axs\_comm tool.

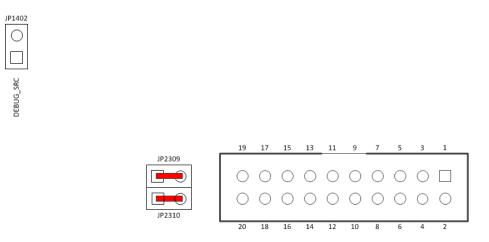

## 2.5 JTAG Programming Header

The JTAG In and JTAG Out interfaces are connected to the CPLD device, which performs JTAG chaining of these multiple targets. These JTAG interfaces are automatically chained when the JTAG Out header is connected to another 10-pin JTAG header at which pin 2 is connected to a 3V3 level.

Optionally, JTAG In can be used to install firmware updates and is typically connected to a Xilinx programming cable. JTAG Out allows including another board (such as a HAPS system) in the JTAG chain. However, firmware updates are usually installed via the USB\_Dataport. Only the USB cable included in the product package is required for this method. Additionally, the package also includes batch scripts and installation instructions.

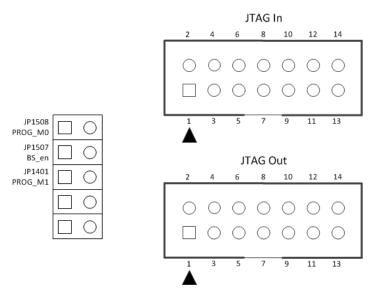

Figure 7 Location of the JTAG In and JTAG Out connectors and the corresponding jumpers

Figure 7 shows the location of the JTAG In and JTAG Out connectors and the related jumpers on the ARC SDP Mainboard. Figure 8 shows the pinout diagrams of the

connectors. Table 7 and Table 8 provide pin descriptions of the JTAG In and JTAG Out connectors. The connectors are compatible with Xilinx programming cables.

Figure 8 Pinout diagrams of the JTAG In and JTAG Out connectors

**Note** The jumpers JP1401, JP1507 and JP1508 shall be out for normal operation.

| Table 7 | Pin description of the JTAG In connector |                                                                          |           |

|---------|------------------------------------------|--------------------------------------------------------------------------|-----------|

| Pin     | Name                                     | Description                                                              | Direction |

| 1       | GND                                      | Ground supply pin                                                        |           |

| 2       | VREF                                     | 3V3 reference voltage related to outputs to previous board in JTAG chain | Output    |

| 3       | GND                                      | Ground supply pin                                                        |           |

| 4       | TMS                                      | Test mode select                                                         | Input     |

| 5       | GND                                      | Ground supply pin                                                        |           |

| 6       | TCK                                      | Test clock                                                               | Input     |

| 7       | GND                                      | Ground supply pin                                                        |           |

| 8       | TDO                                      | Test data to previous board in JTAG chain                                | Output    |

| 9       | GND                                      | Ground supply pin                                                        |           |

| 10      | TDI                                      | Test data and commands from previous board in JTAG chain                 | Input     |

| 11      | GND                                      | Ground supply pin                                                        |           |

| 12      |                                          | Not connected                                                            |           |

| Pin | Name | Description       | Direction |

|-----|------|-------------------|-----------|

| 13  | GND  | Ground supply pin |           |

| 14  |      | Not connected     |           |

| Table 8 | Pin description of the JTAG Out connector |

|---------|-------------------------------------------|

| 10010 0 |                                           |

| Pin | Name | Description                                                      | Direction |

|-----|------|------------------------------------------------------------------|-----------|

| 1   | GND  | Ground supply pin                                                |           |

| 2   | VREF | Reference voltage related to input from next board in JTAG chain | Input     |

| 3   | GND  | Ground supply pin                                                |           |

| 4   | TMS  | Test Mode Select                                                 | Output    |

| 5   | GND  | Ground supply pin                                                |           |

| 6   | TCK  | Test Clock                                                       | Output    |

| 7   | GND  | Ground supply pin                                                |           |

| 8   | TDO  | Test Data read back from next board in JTAG chain                | Input     |

| 9   | GND  | Ground supply pin                                                |           |

| 10  | TDI  | Test data and commands to next board in JTAG chain               | Output    |

| 11  | GND  | Ground supply pin                                                |           |

| 12  |      | Not connected                                                    |           |

| 13  | GND  | Ground supply pin                                                |           |

| 14  |      | Not connected                                                    |           |

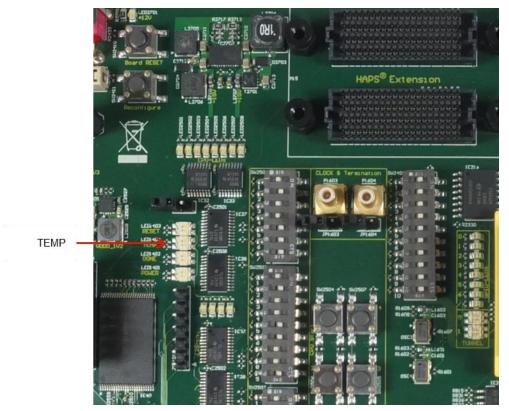

## 2.6 FPGA Temperature and Fan Control

The temperature of the on-board FPGA is monitored by a MAX6670 device. A fan is mounted on top of the FPGA and automatically turned on when the FPGA temperature reaches a certain trigger level.

The LED TEMP changes from green to red when the FPGA temperature becomes too high.

- 75 °C, 167 °F  $\rightarrow$  TEMP LED constant RED

- 90 °C, 194 °F  $\rightarrow$  TEMP LED flashing RED

When this LED turns RED, the user should power down the board and investigate the root cause of this overheating. Figure 9 shows the location of the LED on the ARC SDP Mainboard.

Figure 9 Location of the TEMP LED

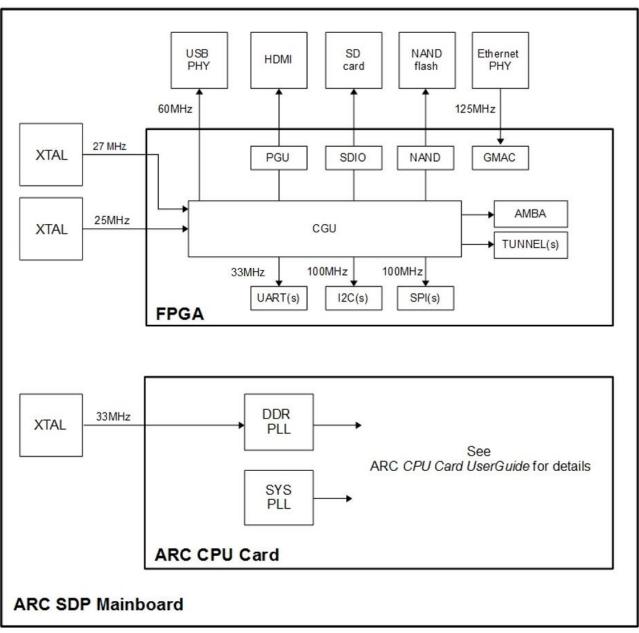

## 2.7 Clock Generation

The ARC SDP Mainboard internally generates all the required clocks. A high level overview of the ARC SDP Mainboard clock architecture is shown in Figure 10. The majority of the required clocks are generated by the Clock Generation Unit inside the FPGA.

Figure 10 Mainboard clock architecture

### 2.7.1 FPGA Reference Clock

The ARC SDP Mainboard contains a 25 MHz and a 27 MHz FPGA input reference clock.

### 2.7.2 AMBA Clocks

The Clock Generation Unit inside the FPGA generates <u>fixed</u> clocks for the AMBA interconnect network. The frequencies for the AMBA interconnect network are listed in Table 9:

| Table 9 A | MBA clocks |

|-----------|------------|

|-----------|------------|

| Clock Name | Frequency (MHz) |  |

|------------|-----------------|--|

| APB clock  | 100             |  |

| AXI clock  | 100             |  |

#### 2.7.3 Tunnel Clocks

The Clock Generation Unit inside the FPGA generates programmable clocks for the two AXI tunnels. The default frequencies for the AXI tunnels (before and after loading the bootloader) are listed in Table 10 and Table 11.

See the "Clock Generation Registers" section for details on programming the AXI tunnel clocks for different frequencies.

Table 10AXI tunnel clocks (after reset)

| Clock Name                   | Frequency (MHz) | Remarks               |

|------------------------------|-----------------|-----------------------|

| Tunnel clock 0 (CPU Card)    | 25              | Max. frequency 100MHz |

| Tunnel clock 1 (HAPS system) | 25              | Max. frequency 75MHz  |

Table 11AXI tunnel clocks (after pre-boot)

| Clock Name                   | Frequency (MHz) | Remarks               |

|------------------------------|-----------------|-----------------------|

| Tunnel clock 0 (CPU Card)    | 100             | Max. frequency 100MHz |

| Tunnel clock 1 (HAPS system) | 25              | Max. frequency 75MHz  |

### 2.7.4 PGU Clock

The Clock Generation Unit inside the FPGA generates a programmable reference clock for the PGU. The PGU reference clock frequency is dependent on the target HDMI resolution. The default frequencies for the PGU reference clock (before loading the bootloader) is listed in Table 12.

See the "Clock Generation Registers" section for details on programming the PGU reference clock to different frequencies.

Table 12PGU reference clock

| Clock Name          | Frequency (MHz) | Remarks                 |  |

|---------------------|-----------------|-------------------------|--|

| PGU reference clock | 74.25           | Max. frequency 74.25MHz |  |

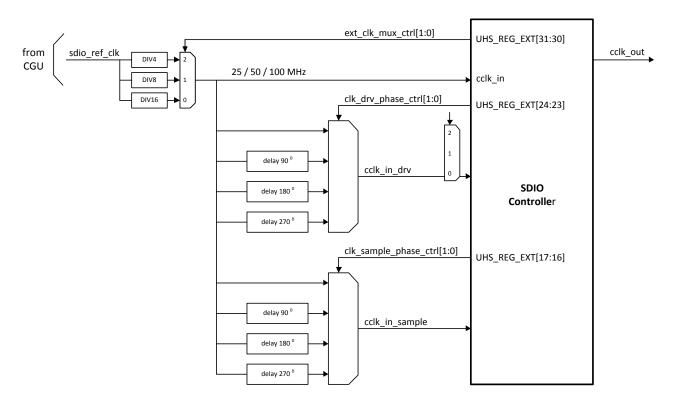

### 2.7.5 Storage Clocks

The Clock Generation Unit inside the FPGA generates <u>fixed</u> reference clocks for the storage IP (i.e. SDIO, and NAND). The desired operating storage speed can be programmed in the peripheral. The frequencies for the storage connectivity reference clocks are listed in the table below:

Table 13 Storage reference clocks

| Clock Name           | Frequency (MHz) |

|----------------------|-----------------|

| NAND reference clock | 25              |

| SDIO reference clock | 400             |

Figure 11 Selecting SDIO card clock frequency via the SDIO controller

### 2.7.6 Serial Connectivity Clocks

The Clock Generation Unit inside the FPGA generates fixed reference clocks for the serial connectivity peripherals (i.e. I2C, UART and SPI). The desired operating baudrate can be programmed in the peripheral. The frequencies for the serial connectivity reference clocks are listed in the table below:

| Clock Name                       | Frequency (MHz) |  |

|----------------------------------|-----------------|--|

| UART reference clock             | 33              |  |

| I <sup>2</sup> C reference clock | 100             |  |

| SPI reference clock              | 50              |  |

| SPI_FLASH reference clock        | 100             |  |

Table 14 Serial Connectivity reference clocks

### 2.7.7 Audio Reference Clock

The Clock Generation Unit inside the FPGA generates two fixed audio reference clocks for I2S audio output to HDMI PHY. One of the two reference clocks can be selected by software using the AUDIO CLK MUX CTRL register (see "Control Registers").

See the "Clock Generation Registers" section for details on dividing down the fixed audio reference clock to the desired I2S sclk and mclk frequency.

Table 15 Audio Reference Clocks

| Clock Name                       | Frequency (MHz) |  |

|----------------------------------|-----------------|--|

| 12.288 MHz audio reference clock | 12.288          |  |

| 28.224 MHz audio reference clock | 28.224          |  |

### 2.7.8 ARC CPU Card Clock

The ARC SDP Mainboard generates a fixed 33 MHz clock for the ARC CPU Card.

### 2.8 Ethernet

The ARC SDP Mainboard features a DP83865 Gigabit Ethernet Physical Layer from National Semiconductor and supports the 10/100 Mb/s Ethernet protocols. The PHY is connected to the FPGA using the RGMII interface of this chip. A standard RJ45 connector is used as external interface.

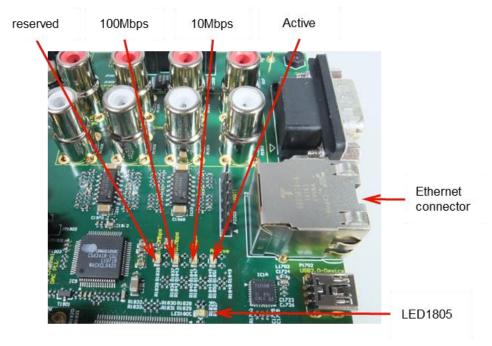

The LEDs related to the Ethernet PHY are listed in Table 16. Figure 12 shows the position of the Ethernet LEDs on the board.

See [7] for functional details of the Ethernet PHY. Refer to the release notes at the ARC SDP download webpage [12] for the driver availability information.

| LED Name<br>(Mainboard) | LED Name<br>(DP83865) | Description                                                      |

|-------------------------|-----------------------|------------------------------------------------------------------|

| Active                  | ACTIVITY_LED          | Indicates the occurrence of either idle error or packet transfer |

| 10Mbps                  | LINK10_LED            | PHY established a good link at 10Mbps                            |

| 100Mbps                 | LINK100_LED           | PHY established a good link at 100Mbps                           |

| LED1805                 | DUPLEX_LED            | PHY is in full duplex operation after the link is established    |

Table 16 Ethernet LEDs

Figure 12 Location of Ethernet connector and Ethernet LEDs

## 2.9 USB

The ARC SDP Mainboard has a USB host interface, which is implemented using a TUSB1210 standalone USB Transceiver Chip [10] from Texas Instruments supporting the USB 2.0 and On-The-Go protocols. The PHY is connected to the FPGA using the ULPI interface. A standard USB A connector is used for the USB host.

The USB miniB connector on the board is reserved for future extensions.

Refer to the release notes at the ARC SDP download webpage [12] for the driver availability information.

### 2.10 HDMI Output

The ARC SDP Mainboard supports HDMI/DVI video output using the HDMI transceiver ADV7511 from Analog Devices [8]. The ADV7511 is a high speed High Definition Multimedia Interface (HDMI) transmitter that is capable of supporting an input data rate up to 165MHz (1080p @ 60Hz, UXGA @ 60Hz) and an output data rate up to 225MHz. The HDMI transmitter is controlled by a PGU (Pixel Graphics Unit) sending 3x8 bits RGB data. The external interface is a standard 19-pin HDMI Plug Type A.

The HDMI transceiver is controlled through its  $I^2C$  interface, which is connected to the internal  $I^2C$  bus. The I2C2 module of the peripheral subsystem and the communication channel of the USB Dataport are masters on this bus. Set the  $I^2C$  address byte to 0xE5 for reading and to 0xE4 for writing.

Refer to the datasheet of the HDMI chip [9] for programming details.

Refer to the release notes at the ARC SDP download webpage [12] for the availability of a driver.

The SPDIF-IN audio interface of the HDMI transceiver is connected to the SPDIF-IN RCA connector. Furthermore, the 8-channel I<sup>2</sup>S master input of the HDMI transceiver is connected to an I2S device in the FPGA on the Mainboard. See the "HDMI Audio Content" sub-section below for details on the HDMI audio interfacing options.

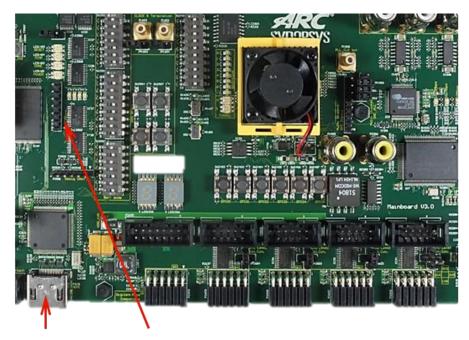

Figure 13 shows the location of HDMI-related connectors on the Mainboard.

HDMI HDMI 8-Channel I2S In

Figure 13 Location of HDMI-related connectors and jumpers on the Mainboard

### 2.10.1 HDMI Audio Content

The HDMI audio content can be provided by the SPDIF-IN RCA plug, or by the I<sup>2</sup>S master mapped in the FPGA on the Mainboard. The HDMI transceiver chip SPDIF-out is left unconnected.

### 2.10.1.1 Using HDMI I2S Audio Source Input

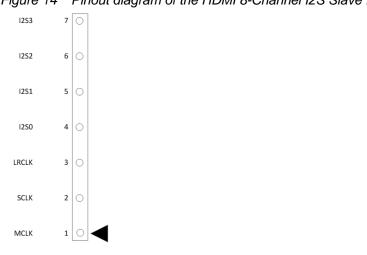

The I2S audio input of the HDMI transmitter is connected to a Multi-Channel I2S device in the PSS of the FPGA on the Mainboard. Table 17 provides the pin description of the HDMI 8-channel I<sup>2</sup>S slave input and Figure 14 shows the pinout diagram of the HDMI 8-channel I<sup>2</sup>S slave input. Figure 13 on page 35 shows the location of the HDMI connector and the HDMI 8-Channel I2S In connector on the Mainboard.

Changing the HDMI audio source also requires re-programming the HDMI transceiver chip.

| Pin | Name   | Description                                  | Direction |

|-----|--------|----------------------------------------------|-----------|

| 1   | MCLK   | HDMI multi-channel oversampling clock        | Input     |

| 2   | SCLK   | HDMI multi-channel bit clock                 | Input     |

| 3   | LRCLK  | Multi-channel word select (left/right clock) | Input     |

| 7-4 | I2S3-0 | Multi-channel data 3-0                       | Input     |

Table 17 Pin Description of the HDMI 8-Channel I<sup>2</sup>S Slave Input

Figure 14 Pinout diagram of the HDMI 8-Channel I2S Slave Input (JP2101)

#### 2.10.1.2 Using HDMI SPDIF Audio Input

The SPDIF-IN RCA plug is connected to the ARC CPU card as well as to the SPDIF-IN of the HDMI transceiver chip. The HDMI audio content is provided by this SPDIF-IN RCA plug. Changing the HDMI audio source also requires re-programming the HDMI transceiver chip.

# 2.11 Audio Support

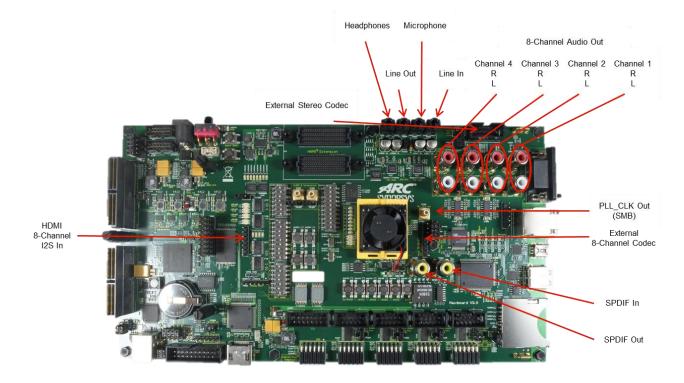

Figure 15 shows the location of the available audio connectors on the board and Table 18 provides a description of the connectors.

Figure 15 ARC SDP Mainboard audio interfaces

The ARC SDP Mainboard includes stereo and eight-channel audio codecs supporting the following analog audio interfaces:

- 7:1 multi-channel line-out (RCA Audio connectors)

- Stereo line out (3.5 mm stereo Jack)

- Headphone out (3.5 mm stereo Jack)

- Stereo line Input (3.5 mm stereo Jack)

- Microphone Input (3.5 mm stereo Jack)

Additionally, the following digital S/PDIF interfaces are available:

- S/PDIF input (RCA plug)

- S/PDIF output (RCA plug)

The digital sources and sinks for these interfaces are routed to the ARC CPU Card. Refer to the documentation of your ARC CPU Card to find out to what extent the CPU Card supports audio.

| Name                        | Description                                                                                                                                                                               | Voltage Level         |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Stereo Line Out             | 3.5 mm female TRS stereo jack for line out                                                                                                                                                |                       |

| Headphones                  | 3.5 mm female TRS stereo jack for headphones output                                                                                                                                       |                       |

| Stereo Line In              | 3.5 mm female TRS stereo jack for line in                                                                                                                                                 |                       |

| Microphone                  | 3.5 mm female TRS stereo jack for microphone input                                                                                                                                        |                       |

| CH1-left                    | RCA jack for channel 1 left                                                                                                                                                               |                       |

| CH1-right                   | RCA jack for channel 1 right                                                                                                                                                              |                       |

| CH2-left                    | RCA jack for channel 2 left                                                                                                                                                               |                       |

| CH2-right                   | RCA jack for channel 2 right                                                                                                                                                              |                       |

| CH3-left                    | RCA jack for channel 3 left                                                                                                                                                               |                       |

| CH3-right                   | RCA jack for channel 3 right                                                                                                                                                              |                       |

| CH4-left                    | RCA jack for channel 4 left                                                                                                                                                               |                       |

| CH4-right                   | RCA jack for channel 4 right                                                                                                                                                              |                       |

| SPDIF In                    | RCA jack for SPDIF input                                                                                                                                                                  |                       |

| SPDIF Out                   | RCA jack for SPIDF output                                                                                                                                                                 |                       |

| PLL_CLK Out                 | SMB jack for audio PLL output                                                                                                                                                             | 3V3                   |

| External Stereo<br>Codec    | 10-pin connector for alternative stereo I <sup>2</sup> S master input and I <sup>2</sup> S master output;                                                                                 | Selectable by jumper: |

|                             | These ports allow using a custom audio codec                                                                                                                                              | 3V3                   |

|                             | instead of the on-board stereo codecs                                                                                                                                                     | 2V5                   |

|                             |                                                                                                                                                                                           | 1V8                   |

| External<br>8-Channel Codec | <ul> <li>8-pin header for 8-channel I<sup>2</sup>S master output.</li> <li>This break-out header allows using a custom audio codec instead of the on-board eight-channel codec</li> </ul> | 3V3                   |

| HDMI 8-Channel<br>I2S In    | 7-pin break-out header for observing 8-channel<br>I <sup>2</sup> S data driven by MultiChannel-I2S device in<br>Main Board FPGA design                                                    |                       |

Table 18 Audio interfaces on the Mainboard

### 2.11.1 Analog Stereo Inputs/Outputs

The ARC SDP Mainboard features stereo audio jacks for Line Out, Headphones, Line In and Microphone. The stereo audio input and output signals are converted using two NXP UDA1380 stereo codecs, which by default provide the interface between the stereo I<sup>2</sup>S ports of the CPU Card and the Line Out, Headphones, Line In and Microphone interfaces of the Mainboard.

One of the codecs is used "DAC-only mode", receives audio data from the stereo I<sup>2</sup>S master output of the CPU Card and drives the Line Out and Headphones outputs of the Mainboard.

The other codec is used in "ADC-only mode", samples the analog signals on the Line In and Microphone inputs of the Mainboard and provides digital data to the stereo I<sup>2</sup>S master input of the CPU Card. Software selects between the Line In and the Microphone input by programming the audio DAC chip via the internal I<sup>2</sup>C bus.

The ADC part supports audio rates up to 55 kHz, and the DAC part supports up to 100 kHz. The resolution is 24 bits.

The stereo codecs are controlled through their  $l^2C$  interfaces, which are connected to the l2C2 module of the peripheral subsystem via the internal  $l^2C$  bus. To access the control registers of the stereo codecs set the  $l^2C$  address byte to 0x31 (Line In) or to 0x35 (Line Out) for reading and to 0x30 (Line In) or to 0x34 (Line Out) for writing.

The digital I<sup>2</sup>S interfaces of the stereo codecs are routed to the ARC CPU Card connector.

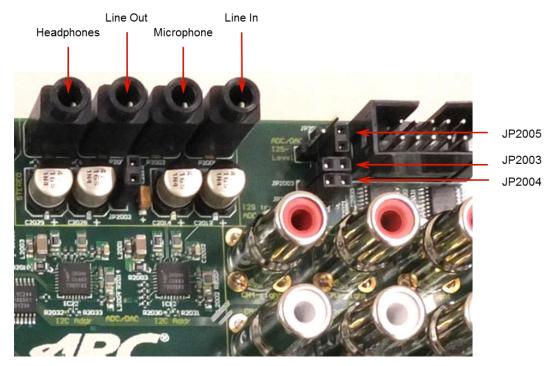

The jumper settings for using the on-board stereo codecs are shown in Figure 16. They correspond to the factory default settings. Figure 17 shows the location of the analog stereo inputs and outputs and of the corresponding jumpers on the Mainboard.

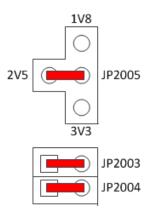

Figure 16 Jumper settings for using the on-board stereo codecs (default)

Figure 17 Location of the stereo inputs and outputs and of the corresponding jumpers

**Note** For advanced use cases, the stereo I<sup>2</sup>S ports of the CPU card can alternatively be connected to custom codecs using the External Stereo Codec connector; see "Using a Custom Stereo Codec".

### 2.11.2 Analog 8-Channel Audio Output

The analog eight-channel audio output is provided through the Cirrus Logic CS42428 or CS42418 audio codec, which supports audio rates up to 192 kHz. The codec has an integrated PLL and supports four multi-bit analog-to-digital and eight multi-bit digital-to-analog delta-sigma converters. The ADCs of this device are not used, however. The outputs of the eight-channel DAC are routed through individual unity-gain low pass filters, which are each

AC-coupled to an RCA audio jack. The low pass filters are implemented using the Texas Instruments LME49740 operational amplifiers.

The eight-channel codec is controlled through its I<sup>2</sup>C interface, which is connected to the I2C2 module of the peripheral subsystem via the internal I<sup>2</sup>C bus. Set the I<sup>2</sup>C address byte to 0x9D for reading the control registers of the eight-channel codec and set the address byte to 0x9C for writing the registers.

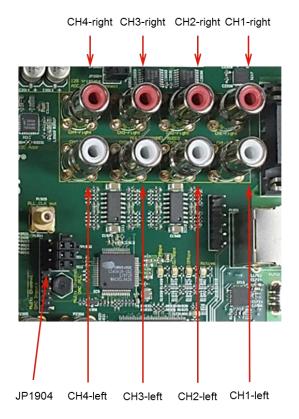

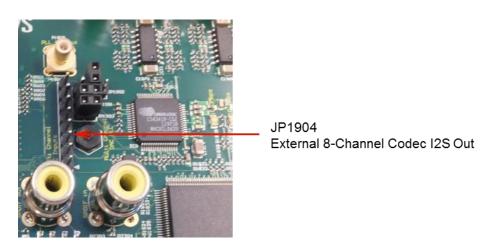

The digital I<sup>2</sup>S interface of the eight-channel codec is routed to the 8-channel I<sup>2</sup>S master output of the ARC CPU Card. Figure 18 shows the location of the interface and of the break-out connector JP1904 on the Mainboard.

For advanced use cases, the 8-channel I<sup>2</sup>S master output of the CPU Card can alternatively be connected to an external custom multi-channel audio D/A converter. Refer to the "Using a Custom Multi-Channel D/A Converter" section for details.

Figure 18 Location of the 8-Channel Output and the corresponding jumpers

## 2.11.3 S/PDIF Inputs and Outputs

The ARC SDP Mainboard features two RCA connectors providing an S/PDIF input and an S/PDIF output. These connectors are routed to the S/PDIF interfaces of the CPU Card. Figure 19 shows the location of the S/PDIF connectors on the Mainboard.

SPDIF Out SPDIF In

Figure 19 Location of the S/PDIF connectors

#### 2.11.3.1 S/PDIF Input

The ARC SDP Mainboard routes the S/PDIF input signal from the RCA jack SPDIF In to the S/PDIF input of the CPU Card, which is located at the CPU Card Connector. Furthermore, this SPDIF In signal is also routed to the HDMI Transceiver.

#### 2.11.3.2 S/PDIF Out

The S/PDIF output of the CPU Card, which is located at the CPU Card Connector, is connected to the SPDIF Out RCA output of the ARC SDP Mainboard. The S/PDIF output signal is coupled to the RCA jack using an audio transformer for robustness.

### 2.11.4 Audio PLL

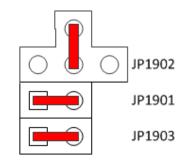

The Cirrus CS42428 Multi-Channel Audio Codec that is used for the analog 8-channel audio output includes a programmable audio PLL.

Figure 20 shows the jumper settings for the audio PLL. Other jumper settings are reserved for future extensions.

The low-jitter PLL follows the PLL reference clock provided by the ARC CPU Card. The PLL clock output (RMCK) and its corresponding lock signal are routed back to the CPU Card. The PLL clock output of the CS42428 is also routed to the SMB clock connector PLL\_CLK Out.

PLL follows a reference clock provided by the ARC CPU Card

Figure 20 Audio PLL jumper settings

The location of these jumpers and of the PLL\_CLK Out connector is shown in Figure 21.

Figure 21 Location of the PLL\_CLK Out connector and of the corresponding jumpers

## 2.11.5 Advanced Audio Use Cases

#### 2.11.5.1 Using a Custom Stereo Codec

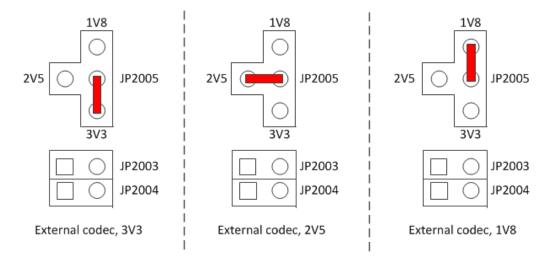

The ARC SDP Mainboard supports using custom audio codecs instead of the on-board codecs. The external codecs should have I<sup>2</sup>S slave interfaces, which operate at 1V8, 2V5 or 3V3 and should be connected to the <code>External Stereo Codec I2S In / Out connector</code>. Figure 22 shows the jumper settings for using an external custom stereo codec and Figure 23 shows the location of the <code>External Stereo Codec I2S In / Out connector</code> and the corresponding jumpers on the Mainboard.

Figure 22 Jumper settings for using an external custom stereo codec

JP2005 JP2003 JP2004

External Stereo Codec I2S In / Out

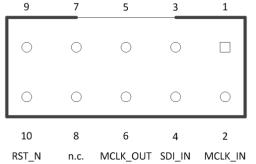

A pin description of the External Stereo Codec I2S In / Out connector is provided in Table 19, and the pinout diagram of the connector is shown in Figure 24.

| Pin | Name     | Description                                | Direction |

|-----|----------|--------------------------------------------|-----------|

| 1   | SCLK_IN  | Stereo input bit clock                     | Output    |

| 2   | MCLK_IN  | Stereo input oversampling clock            | Output    |